| Secciones |

|---|

| Foros Electrónica |

|

|

| Boletines de correo |

|

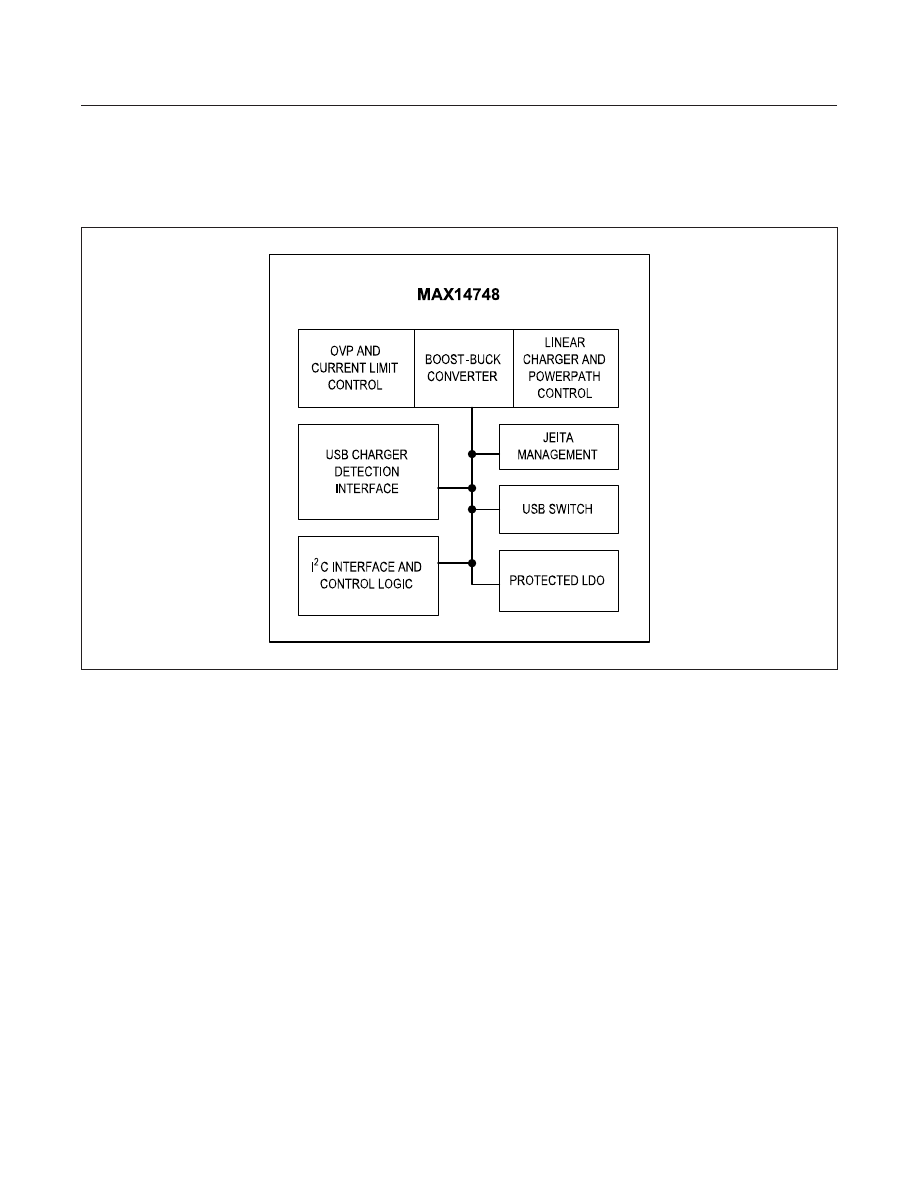

General Description

The MAX14748 USB battery charger integrates a charger

detector, boost/buck converter, and Li+ battery charger

with smart power selector to provide fast and safe charging

of 2s Li+ battery packs.

The MAX14748 provides support for devices functioning

as a UFP/DRP per the USB Type-C 1.1 standard, while

also providing detection of legacy USB Battery Charging

Specification, Revision 1.2 (BC1.2) compliant chargers in

addition to other nonstandard chargers. The programmable

Automatic Input Current Limiting (AICL) feature ensures that

maximum safe current is drawn from the charging adapter.

The Li+ charger includes an automatic Smart Power

Selector™ to simultaneously charge the battery and

provide power to the system load. The Smart Power

Selector function will supplement the system power with

the battery if power from the charging adapter is insufficient.

The Li+ charger features JEITA thermal monitoring and

charger voltage/current reduction or charger disable.

The MAX14748 is available in a 54-bump, 0.4mm pitch,

3.97mm x 2.77mm x 0.64mm wafer-level package (WLP)

and operates over the -40 °C to +85 °C extended temperature

range.

Applications

Digital Imaging (DSC, DVC)

Wireless Speakers

Handheld Barcode Readers

Benefits and Features

Minimize Power Management Footprint Through High

Integration

13mΩ (typ) Integrated Battery To System Switch

Thermal Current Limiting

DC-DC Converter with Boost and Reverse Buck

High Efficiency

- 92% in Boost Mode at 1A Output Current and

7.4V Battery Voltage

- 94% in Reverse Buck Mode at 500mA Output

Internal USB Switch for USB D+/D- Data Lines

Easy-to-Implement Li+ Battery Charging

Charges 2s Li-Ion Batteries from Legacy 5V USB

Adapters

- 15W Input Power with 3A Type-C Adapter

- 7.5W Input Power with DCP Adapter

- 1A System/Charge Current From DCP Adapter

- 2A System/Charge Current From 3A Type-C Adapter

USB Type-C Specification, Rev 1.1 Support

UFP/DRP Operation

V

CONN

and Super-Speed Multiplexer Logic Controls

Non-Standard DCP Detection

USB Battery Charging Specification, Rev 1.2 Compliant

Automatic Input Current Limit (AICL) Power

Management

Support Weak/Dead Batteries Detection

Smart Power Selector

Thermistor Monitor

Various Protection Features

28V Integrated Overvoltage Protection

JEITA Charge Protection

±15kV ESD Protection on USB Adapter Pins

19-100081; Rev 0; 6/17

Smart Power Selector is a trademark of Maxim Integrated

Products, Inc.

MAX14748

USB Type-C Charger

Voltages Referenced to GND

CHGIN ..................................................................-0.3V to +30V

BST .......................................................................-0.3V to +16V

SYS to BAT ..........................................................-0.3V to +12V

BAT, SYS ..............................................................-0.3V to +12V

BYP to CHGIN ......................................................-30V to +0.3V

BYP, THM, INT, SYSOK, FLTIN, FSUS,

LED, SDA, SCL ....................................................-0.3V to 6V

COMP, SET .......................................... -0.3V to V

CCINT

+ 0.3V

CC1, CC2, TDN, TDP, CDN, CDP, V

CONN

............-0.3V to +6V

CC1, CC2, in fault mode through a 10k resistor ..-0.3V to +20V

CDIR .......................................................................-0.3V to +6V

VTPU (VTPU-TPU switch open) .......... -0.3V to V

CCINT

+ 0.3V

TPU (VTPU-TPU switch open) .........-0.3V to 6 or VTPU + 0.3V

VTPU, TPU Maximum Current

(VTPU-TPU switch closed) ...................... -100mA to +100mA

BVCEN ..................................................-0.3V to V

CCINT

+ 0.3V

SFOUT, V

CCINT

, BREG ....... -0.3V to min ((V

CHGIN

+ 0.3), 6)V

LX .............................................................-0.3V to V

SYS

+ 0.3V

NVP ......................................................................-0.3V to +30V

AGND, DGND, PGND, GND ...............................-0.3V to +0.3V

Continuous Current into

CHGIN, SYS ...................................................................+6.4A

BAT .................................................................................+4.8A

Any Other Terminal .....................................................+100mA

Continuous Power Dissipation

(multilayer board at +70 °C): 9 x 6 Array 54-Bump,

3.97mm x 2.77mm 0.4mm Pitch WLP

(derate 24.46mW/ °C) .................................................1.957W

Operating Temperature Range .......................... -40 °C to +85 °C

Junction Temperature ................................................... +150 °C

Storage Temperature Range ........................... -65 °C to +150 °C

Lead Temperature (soldering, 10s) .............................. +300 °C

Soldering Temperature (reflow) .................................... +260 °C

WLP

Junction-to-Ambient Thermal Resistance (Θ

JA

) .....40.88 °C/W

(Note 1)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

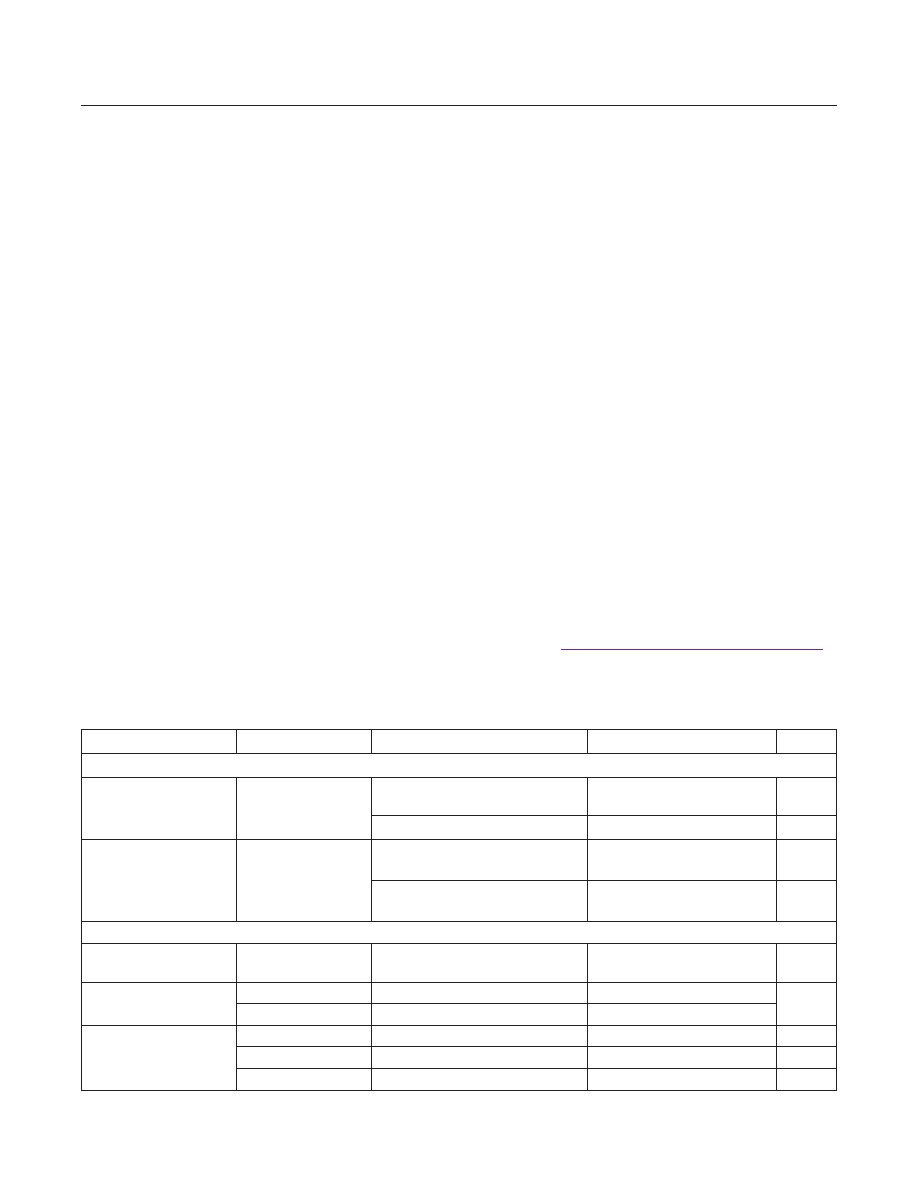

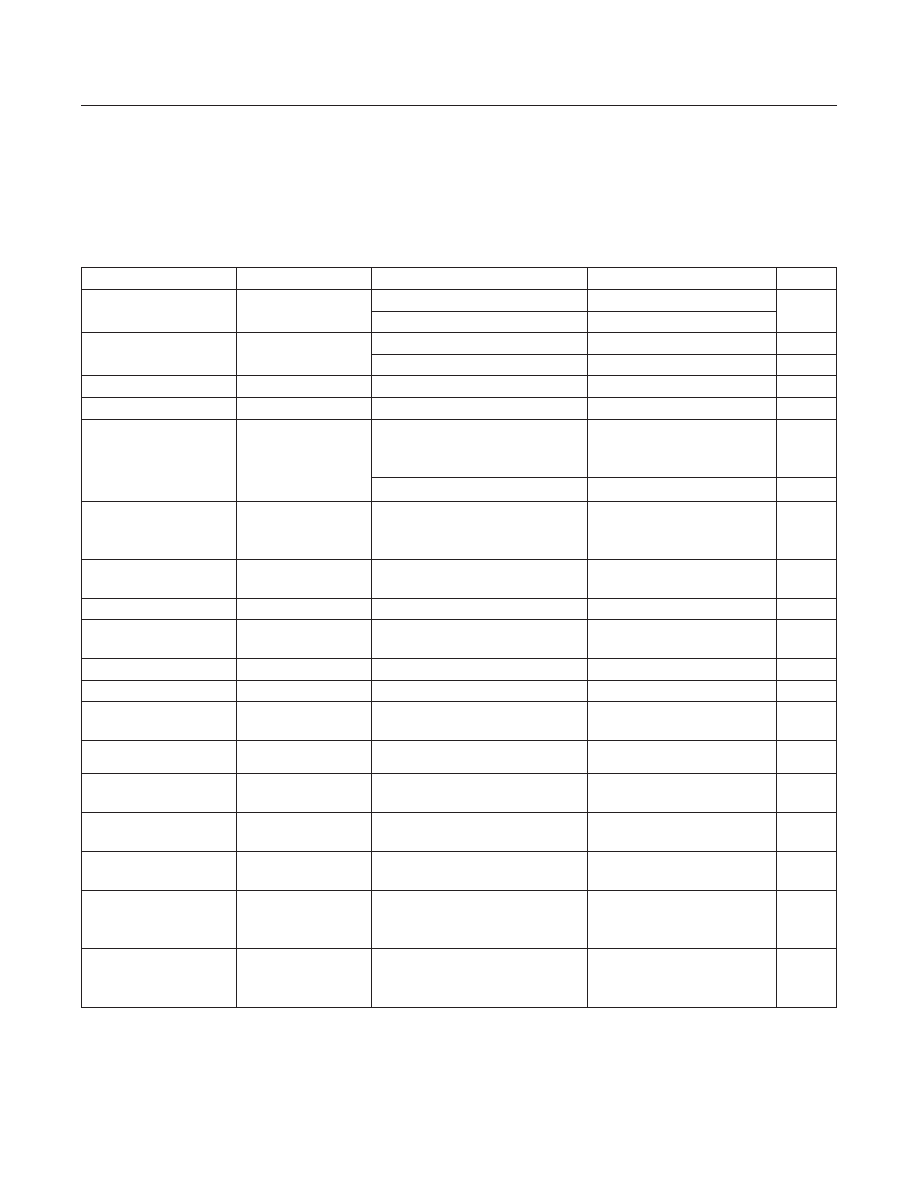

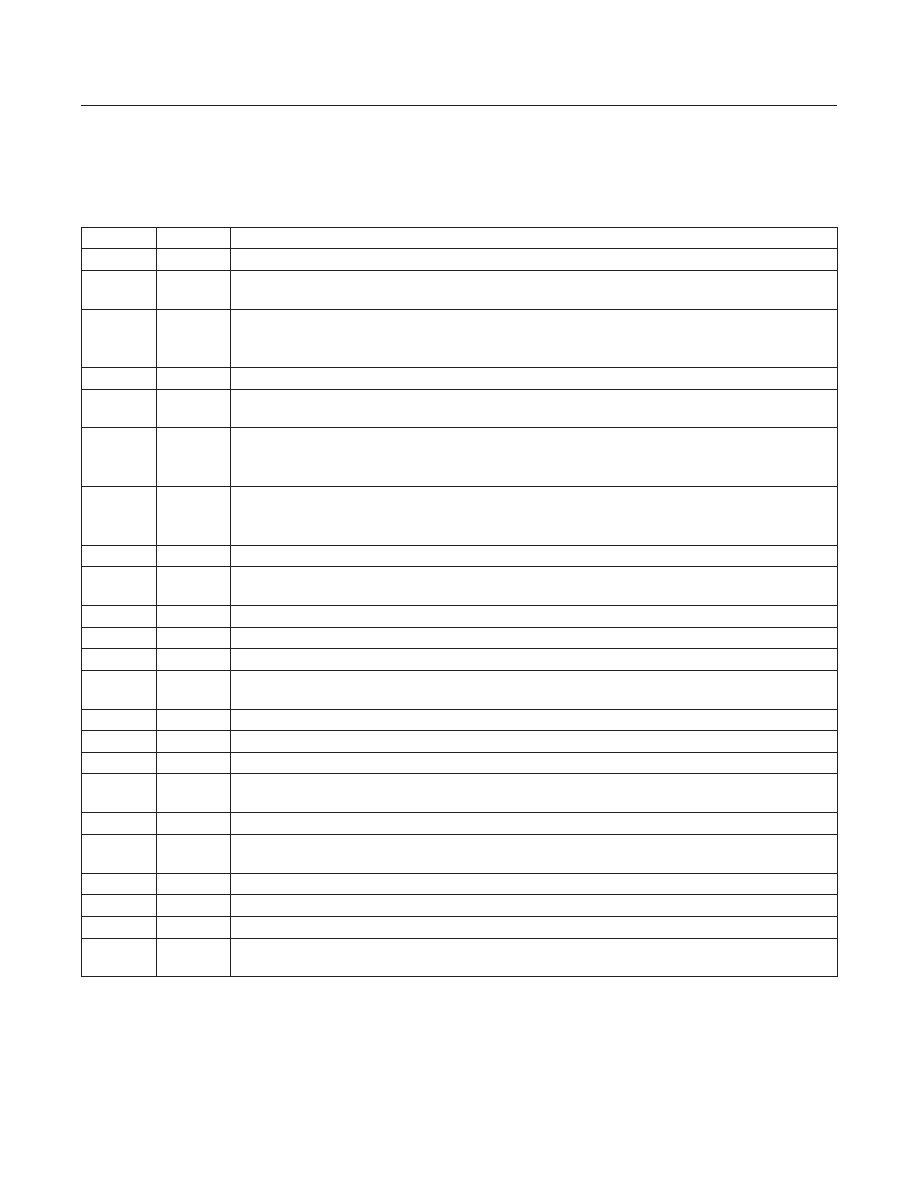

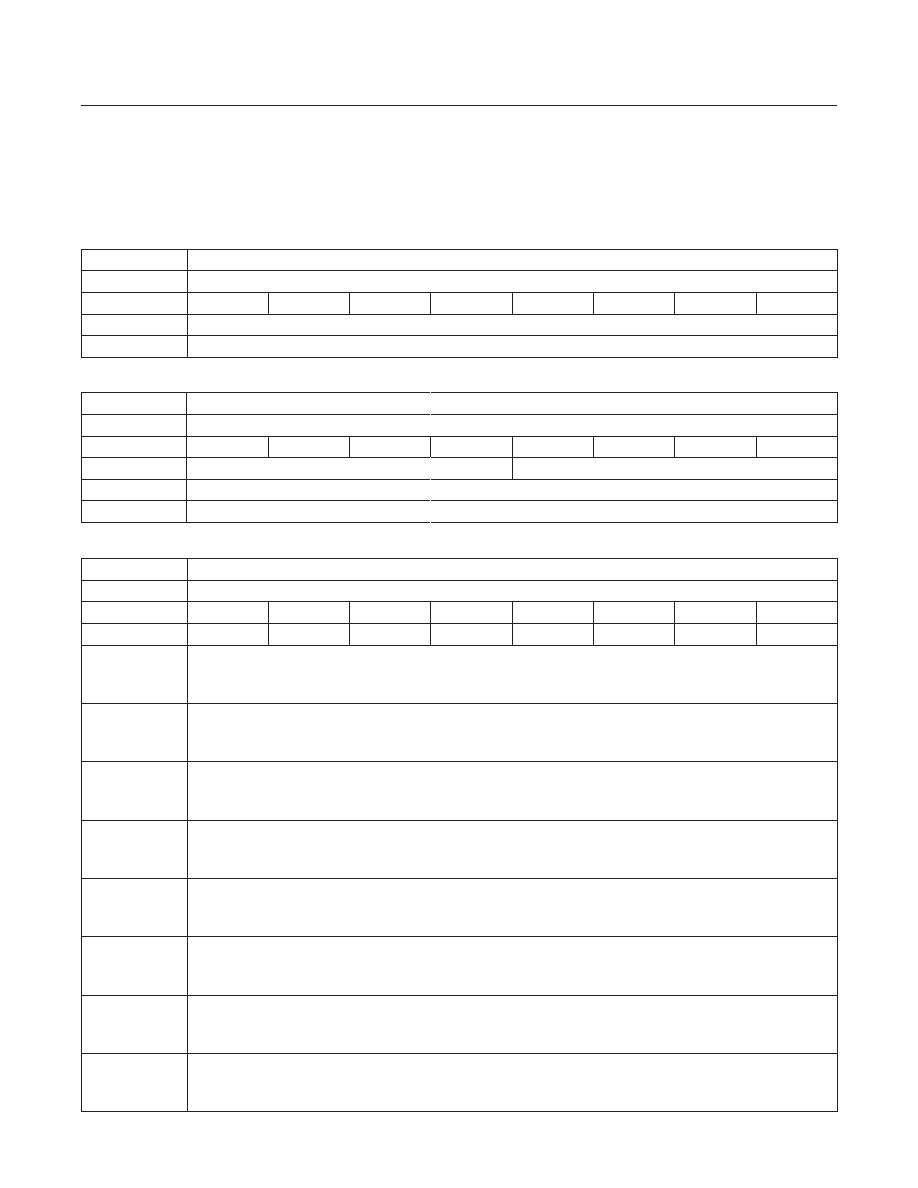

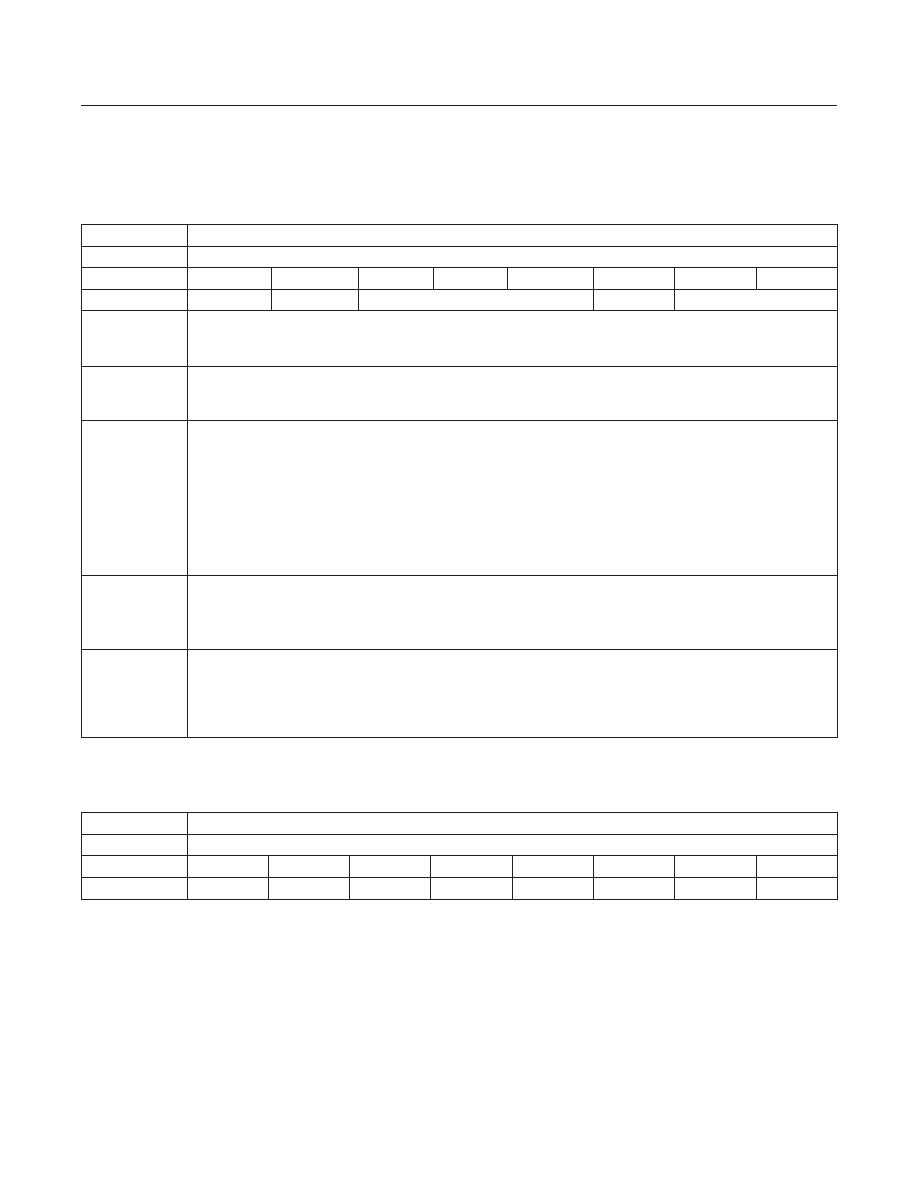

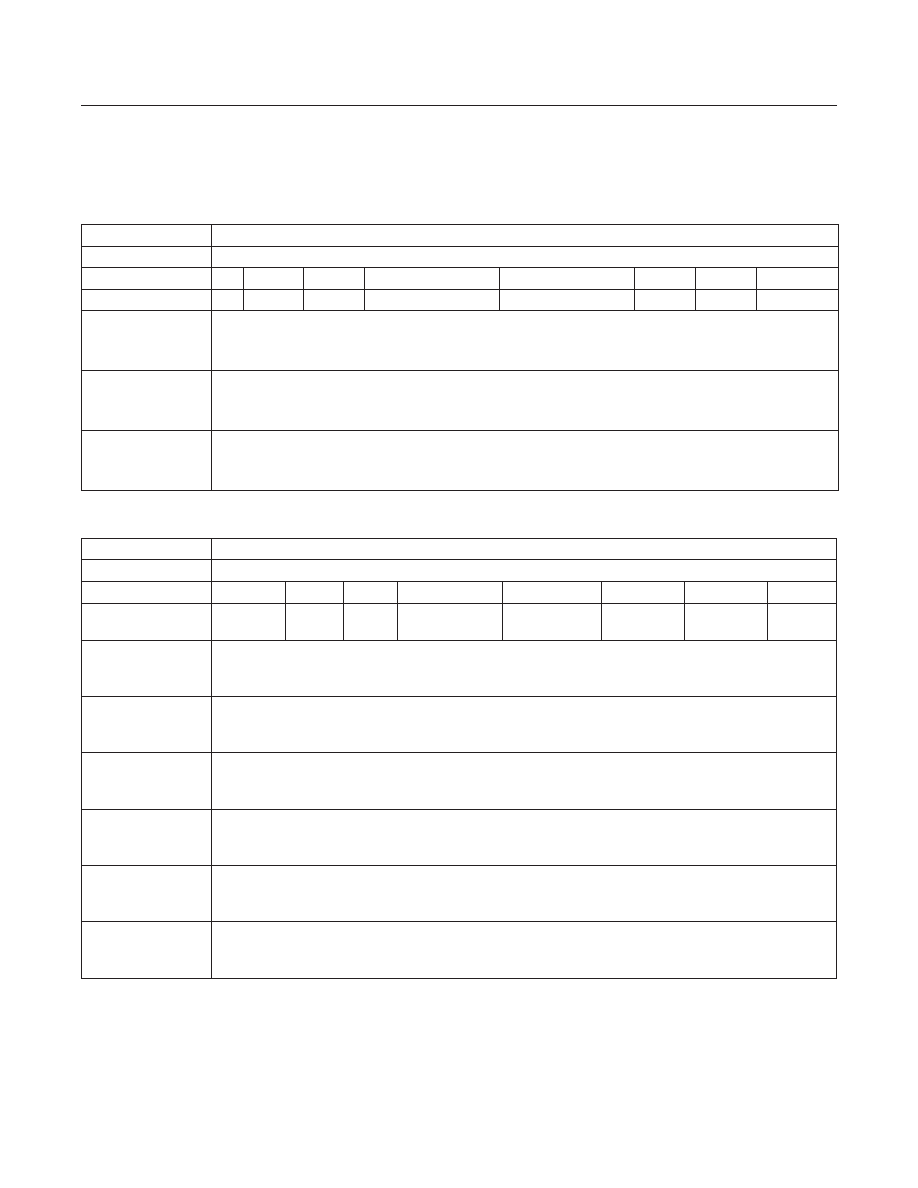

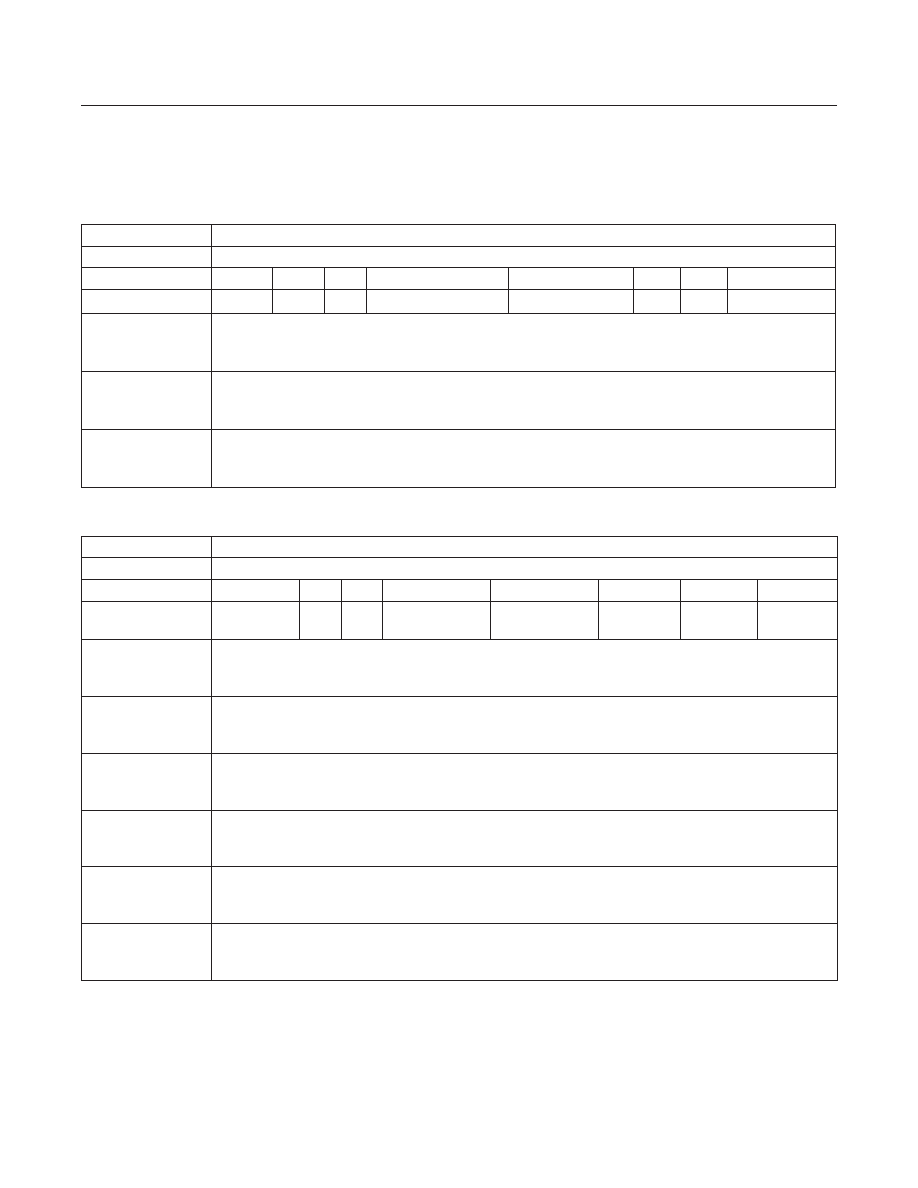

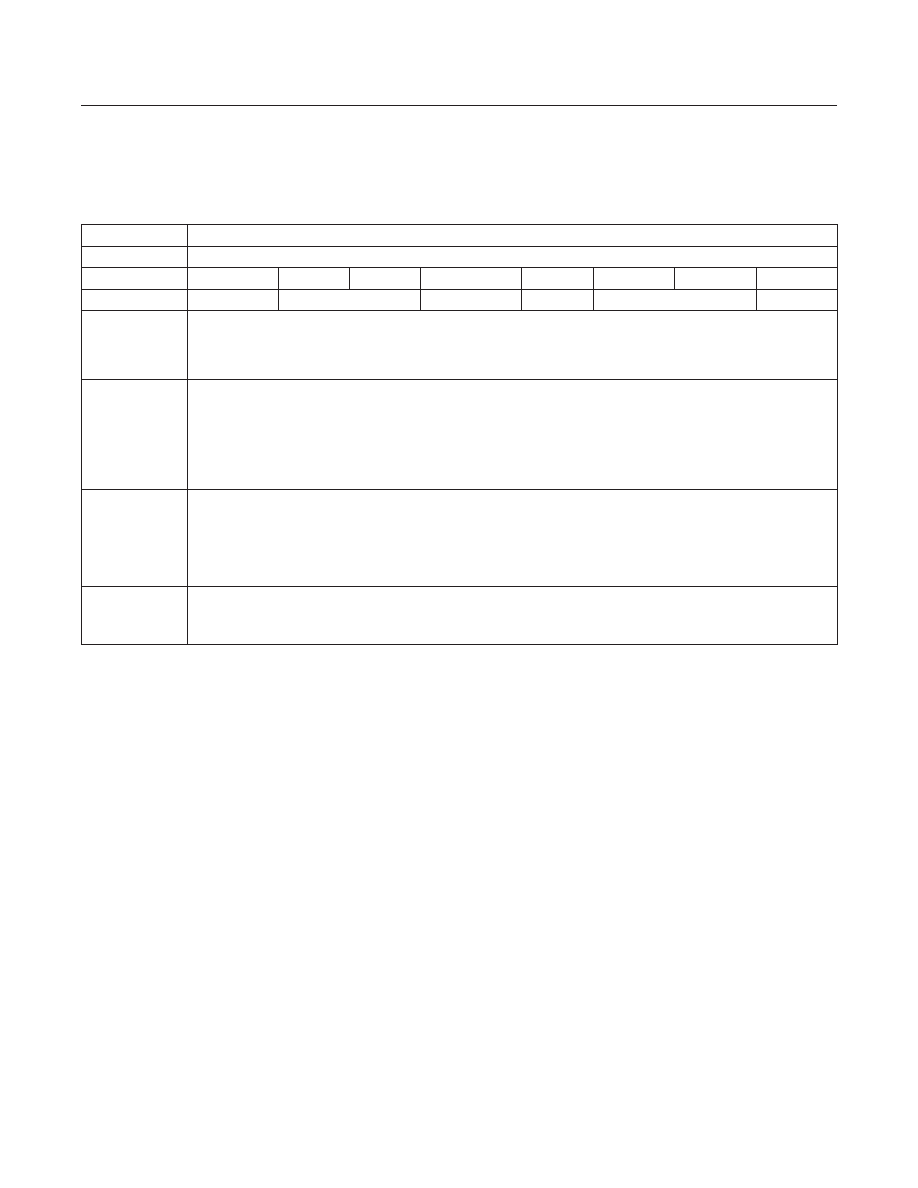

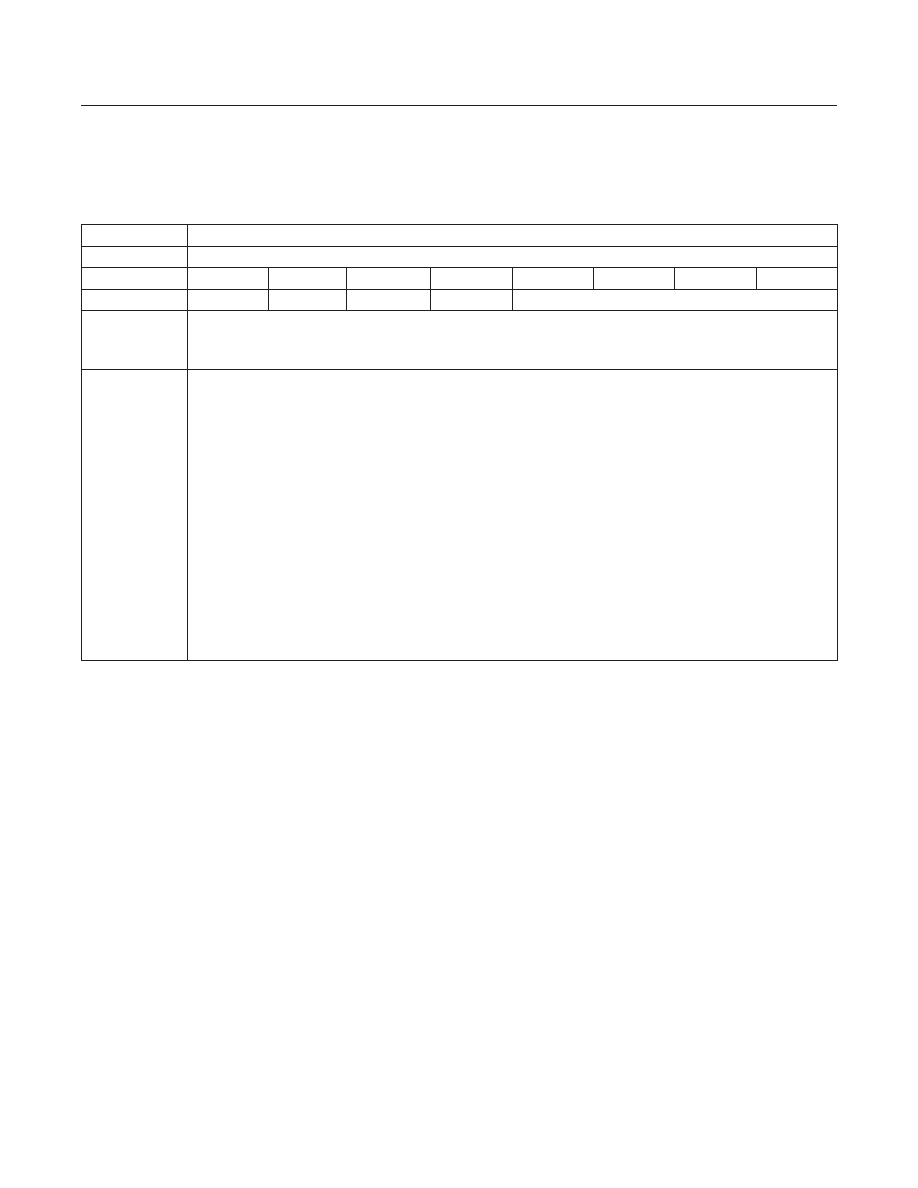

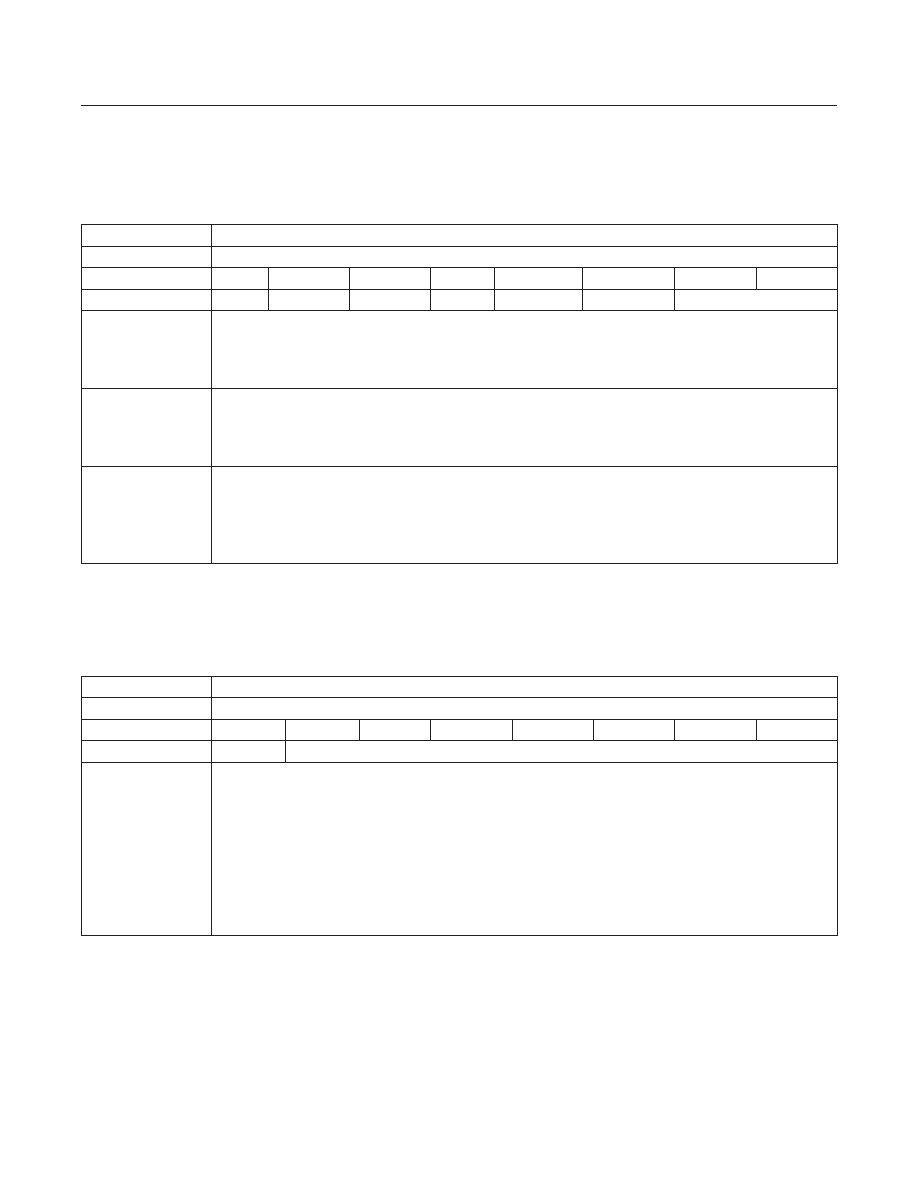

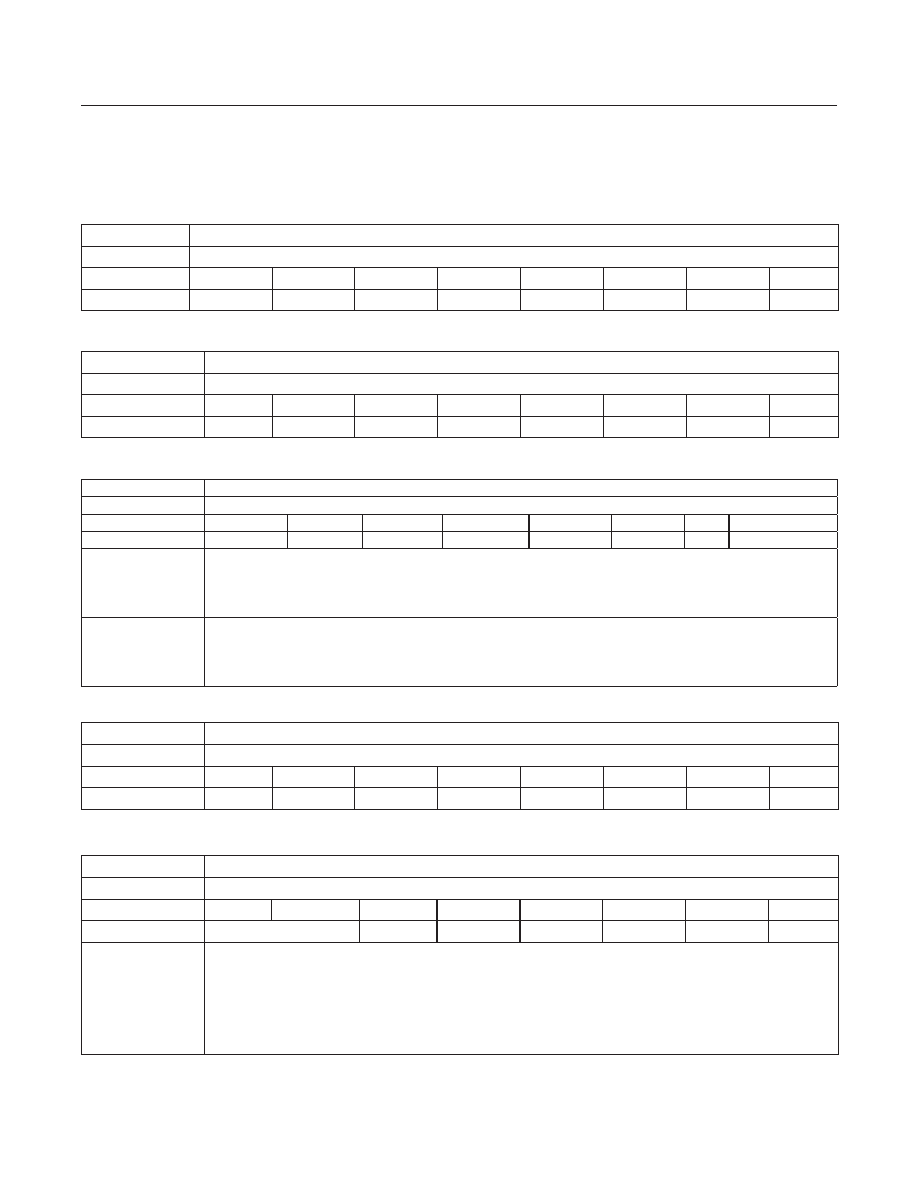

Electrical Characteristics

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SUPPLY CURRENT

BAT Supply Current

I

BAT

V

CHGIN

= 0V or Floating, Type-C

detection active

140

µA

Low Power mode

25

µA

CHGIN Supply Current

I

CHG

V

CHGIN

= +5V, T

A

+25 °C,

ChgEn = 0

5.3

mA

V

CHGIN

= +5V, T

A

+25 °C,

Suspend Mode (FSUS = High)

0.98

mA

CHGIN TO BYP PATH

Allowed CHGIN Input

Voltage Range

V

CHGIN_RNG

0

28

V

CHGIN Detect

Threshold

V

BDET

Rising

3.8

3.9

4.0

V

V

BDET_F

Falling

3.6

3.7

3.8

CHGIN Overvoltage

Threshold

V

OVP

Rising

5.59

5.66

5.72

V

V

OVP_F

Falling

5.56

V

V

OVP_H

Hysteresis

28

mV

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

2

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer

board. For detailed information on package thermal considerations, refer to

.

Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

Package Thermal Characteristics

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

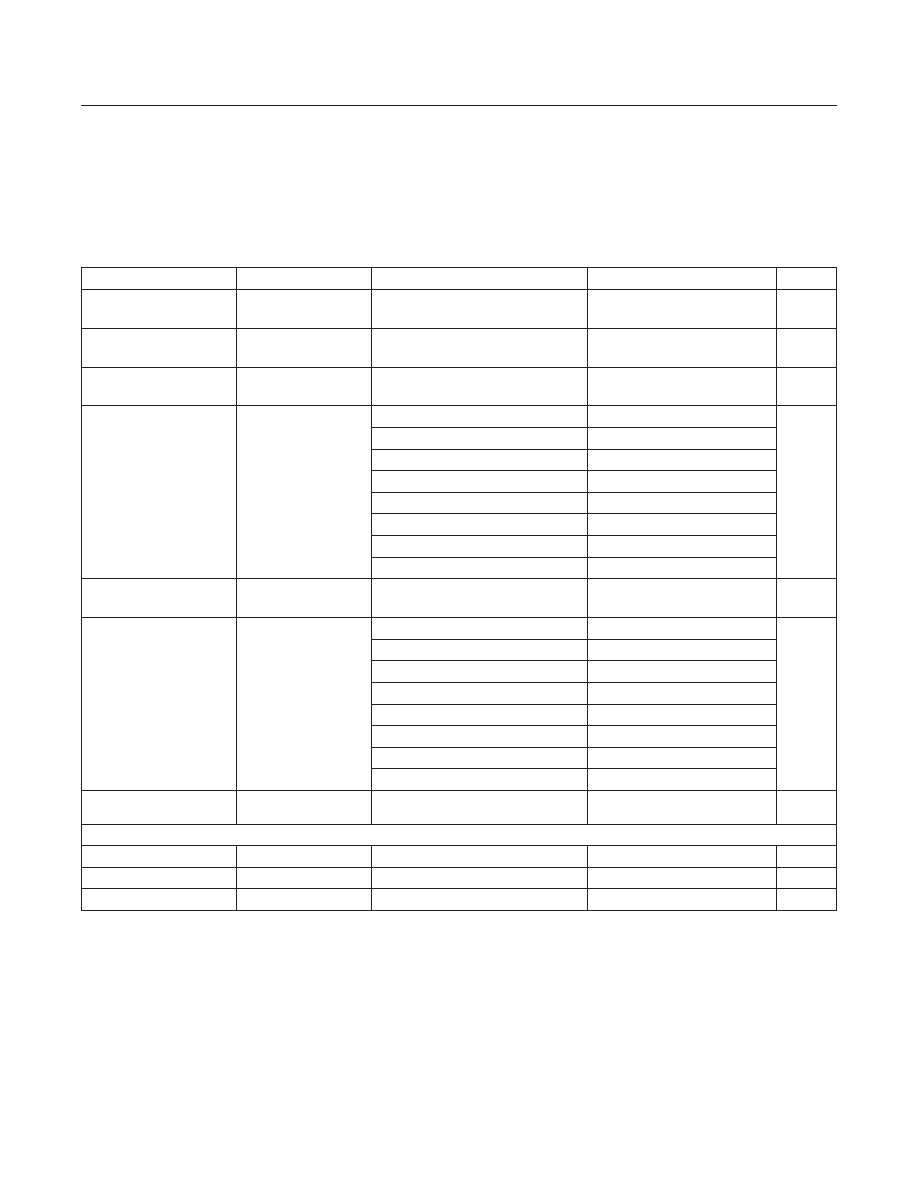

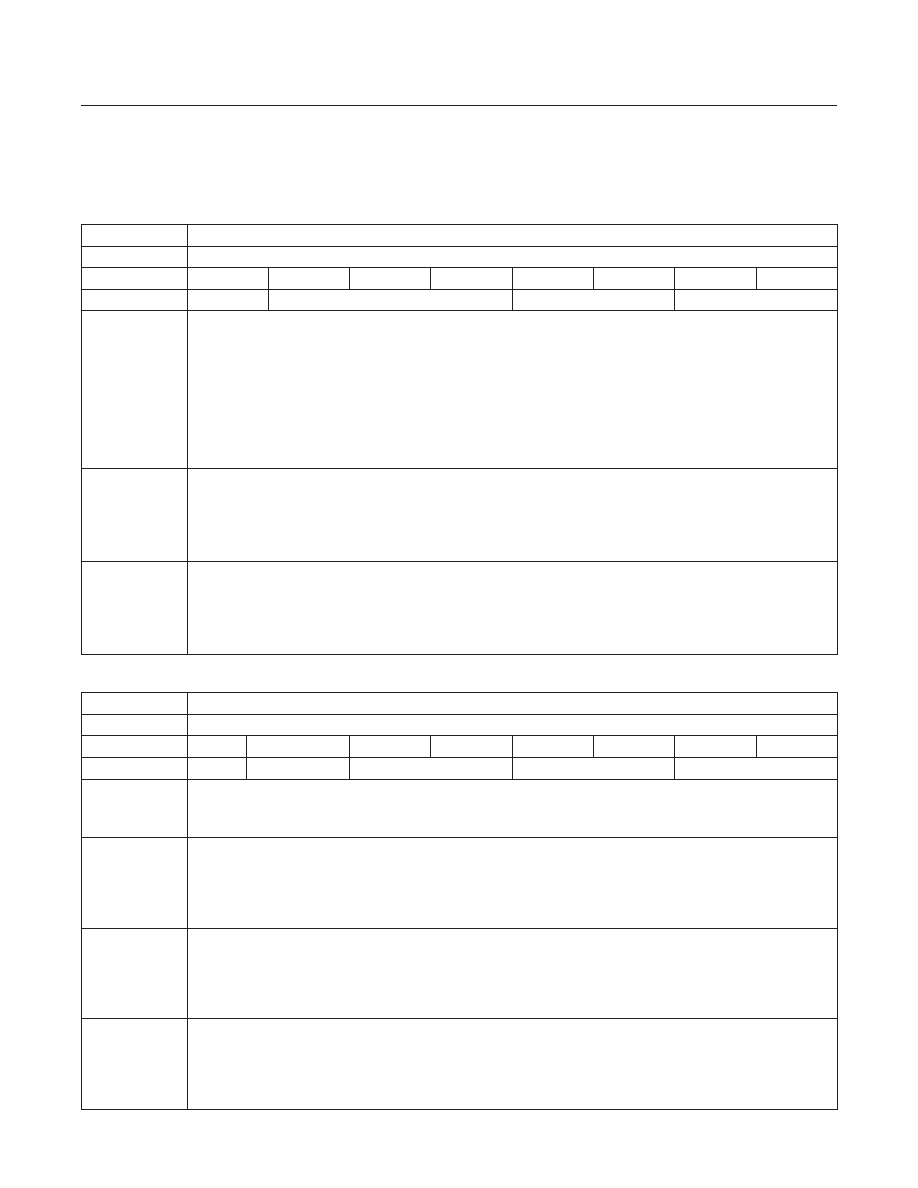

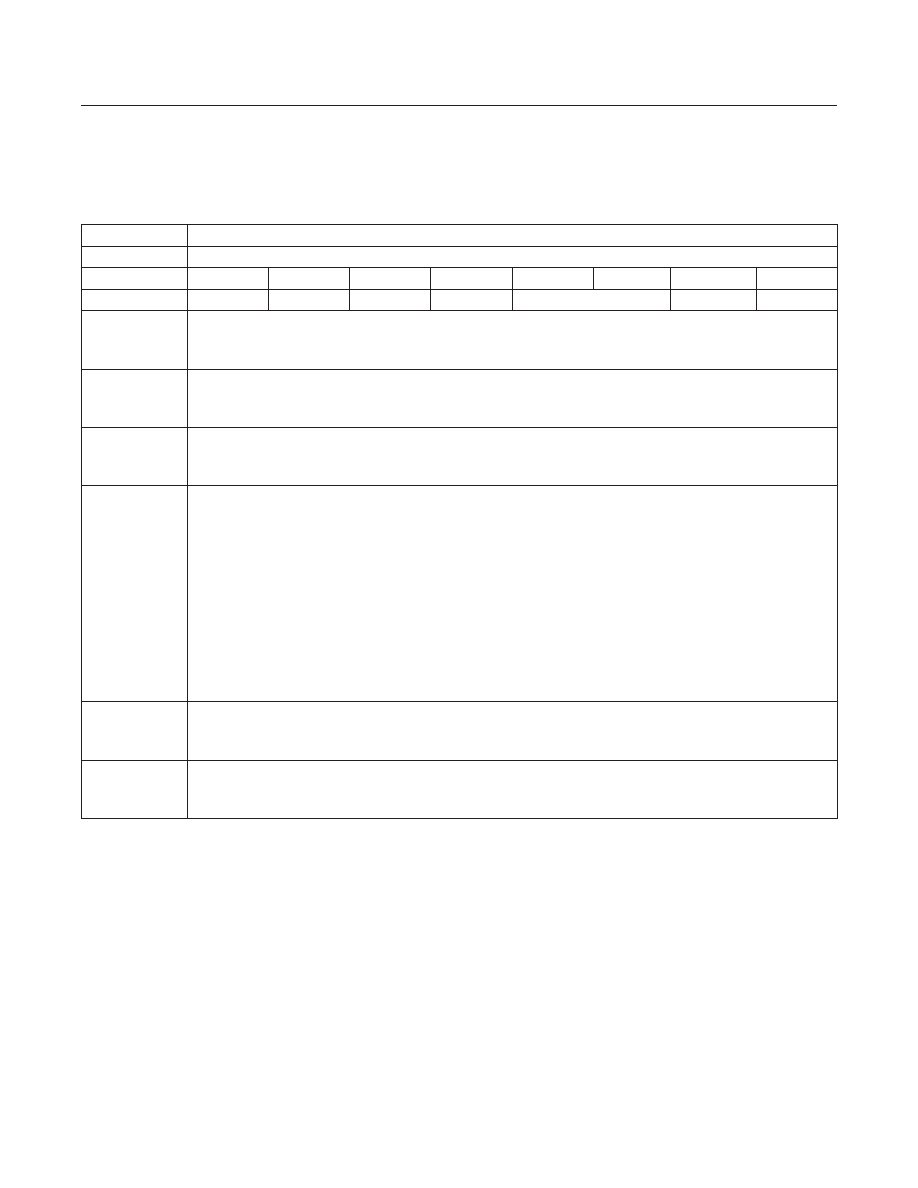

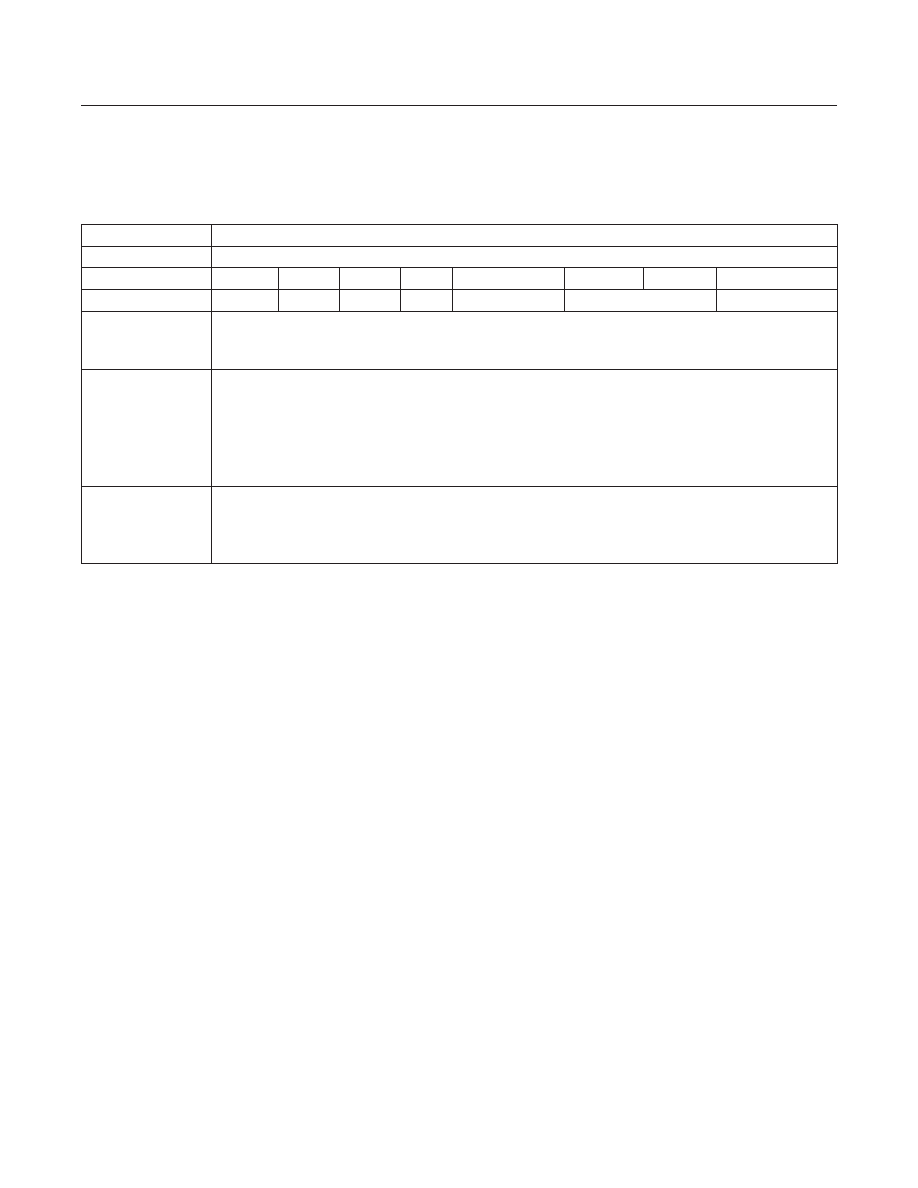

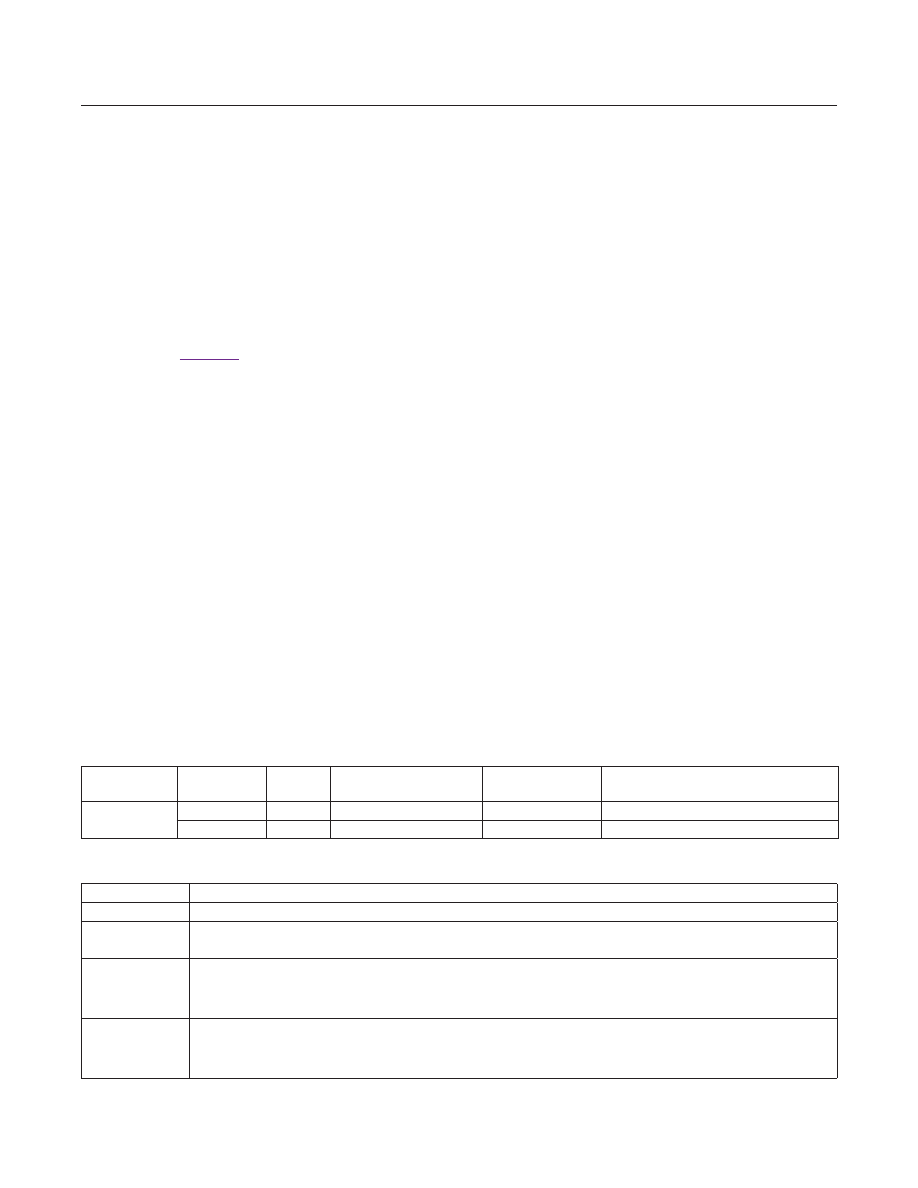

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CHGIN-BYP Resistance

R

CHGIN_BYP

V

CHGIN

= 5V

45

mW

CHGIN-BYP Soft-Start

Timeout

t

BYP_SFTTO

If V

BYP

has not reached within

50mV of V

CHGIN

at timeout, a fault

is flagged by SysFlt of register

0x02.

100

ms

CHGIN-BYP Soft-Start

Current

I

BYP_SFT

60

mA

CHGIN-BYP Soft-Start

End Comparator

V

BYP_SFTEND

15

50

80

mV

CHGIN-BYP Overload

Comparator

V

BYP_OVL

290

360

420

mV

Input Current Limit

I

LIM

SpvChgILim[4:0] = 00100

0.4

A

SpvChgILim[4:0] = 01110

1.5

SpvChgILim[4:0] = 11101

3

Input Current Limit

Programming Range

I

LIM_RNG

0.1

3

A

Input Current Limit

Programming Step

I

LIM_STEP

100

mA

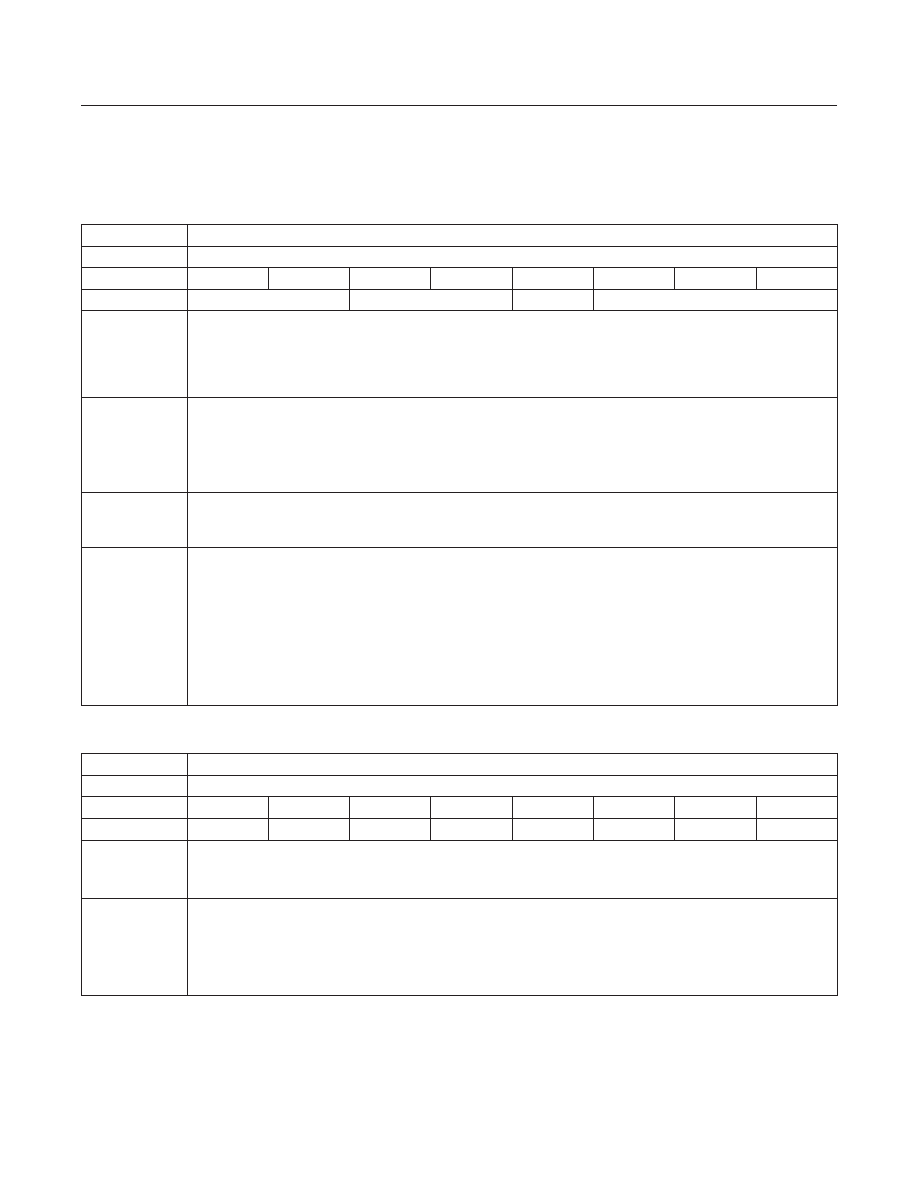

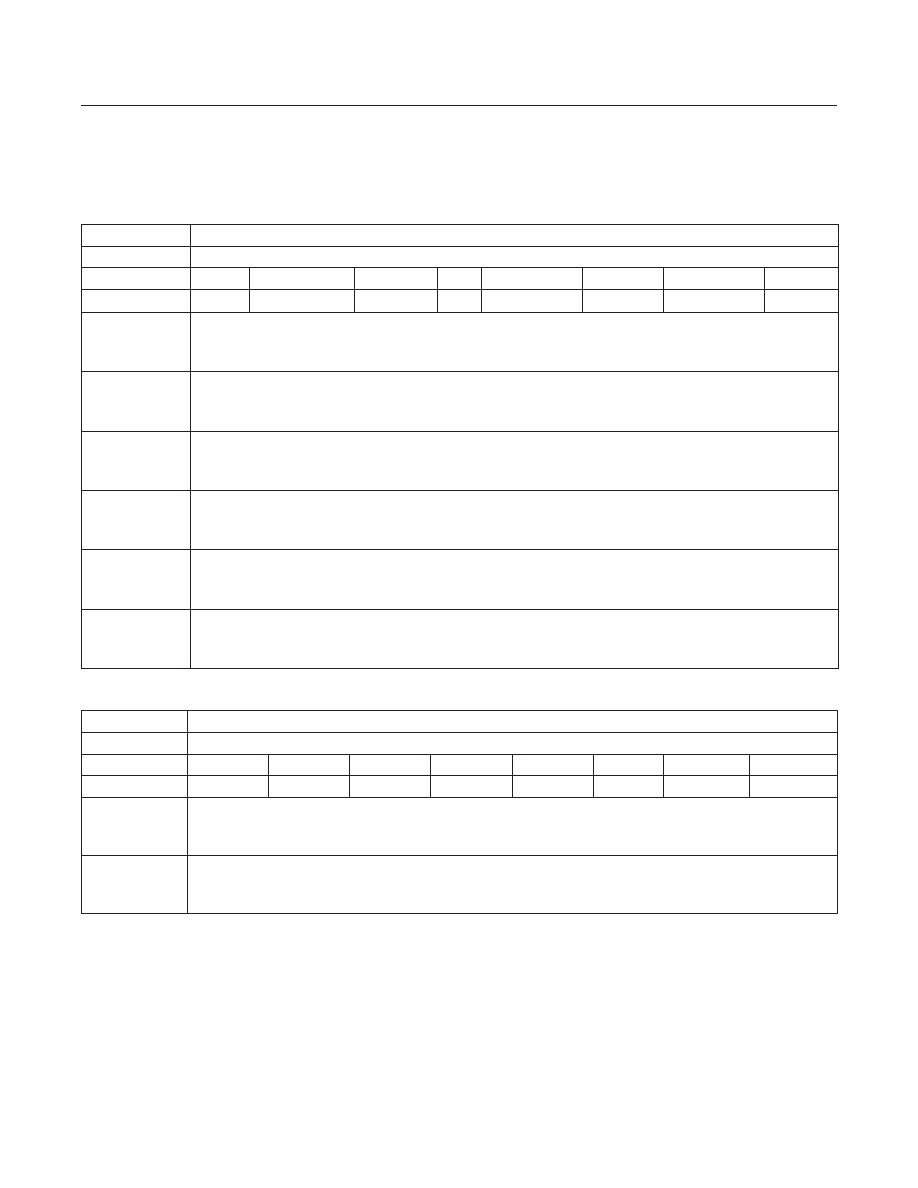

INTERNAL SUPPLIES

Internal V

CCINT

Regulator

V

CCINT

V

CHGIN

= 5V, boost off

4.0

4.3

4.6

V

Boost Regulator BREG

V

BREG

4.3

V

V

CCINT

UVLO

Threshold

V

UVLO

V

CCINT

rising

3.1

3.4

3.7

V

V

CCINT

falling

3.0

3.3

3.6

V

CCINT

UVLO

Threshold Hysteresis

V

UVLO_HYS

Hysteresis

100

mV

BAT UVLO Threshold

V

BATUVLO

Rising

4

V

BAT UVLO Hysteresis

V

BATUVLO_H

100

mV

SFOUT LDO Voltage

V

SFOUT

SfOutLvl = 1, V

CHGIN

= 6V,

I

SFOUT

= 0

3.15

3.3

3.45

V

SfOutLvl = 1, V

CHGIN

= 6V,

I

SFOUT

= 15mA

2.95

SfOutLvl = 0, V

CHGIN

= 6V,

I

SFOUT

= 0

5.0

5.25

5.5

SfOutLvl = 0, VCHGIN = 6V,

I

SFOUT

= 15mA

4.9

SFOUT Maximum

Current

I

SFOUT_MAX

15

mA

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

3

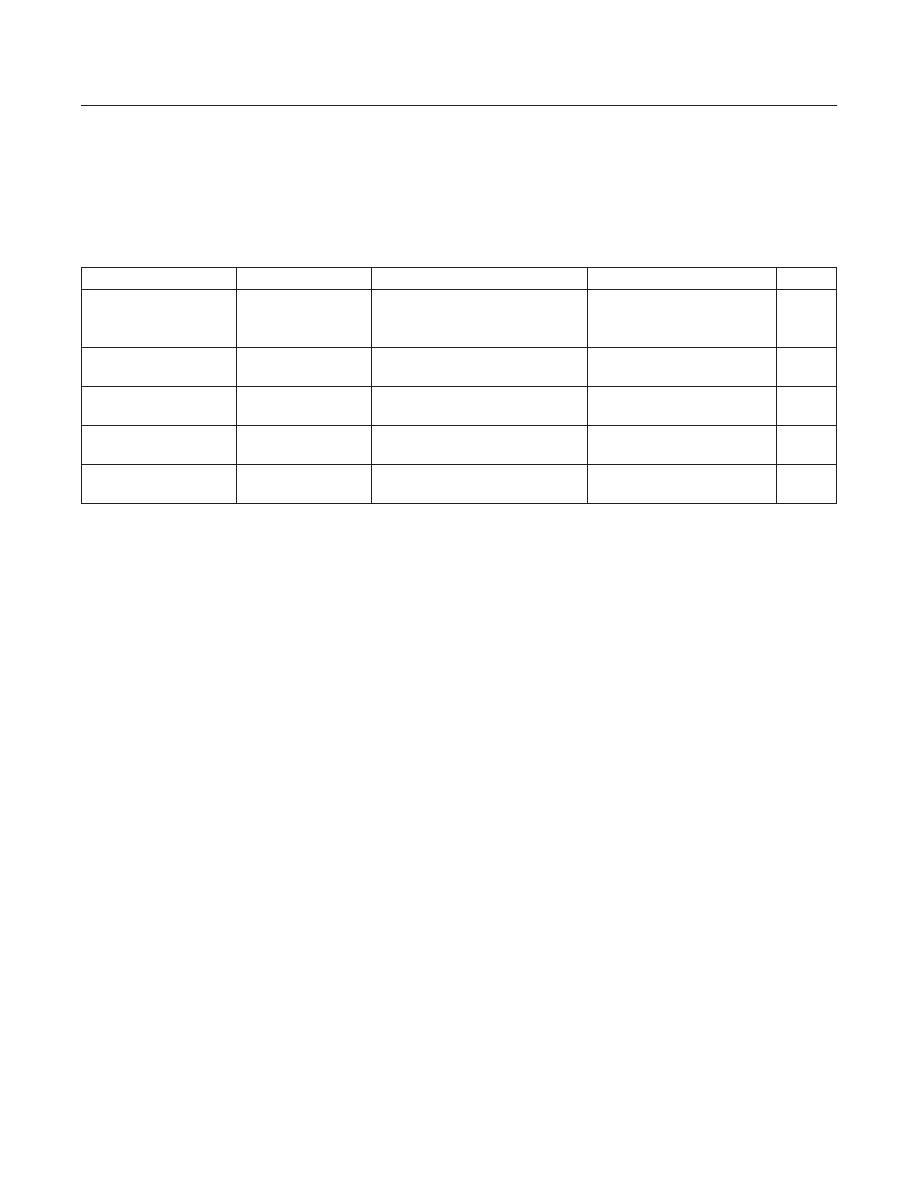

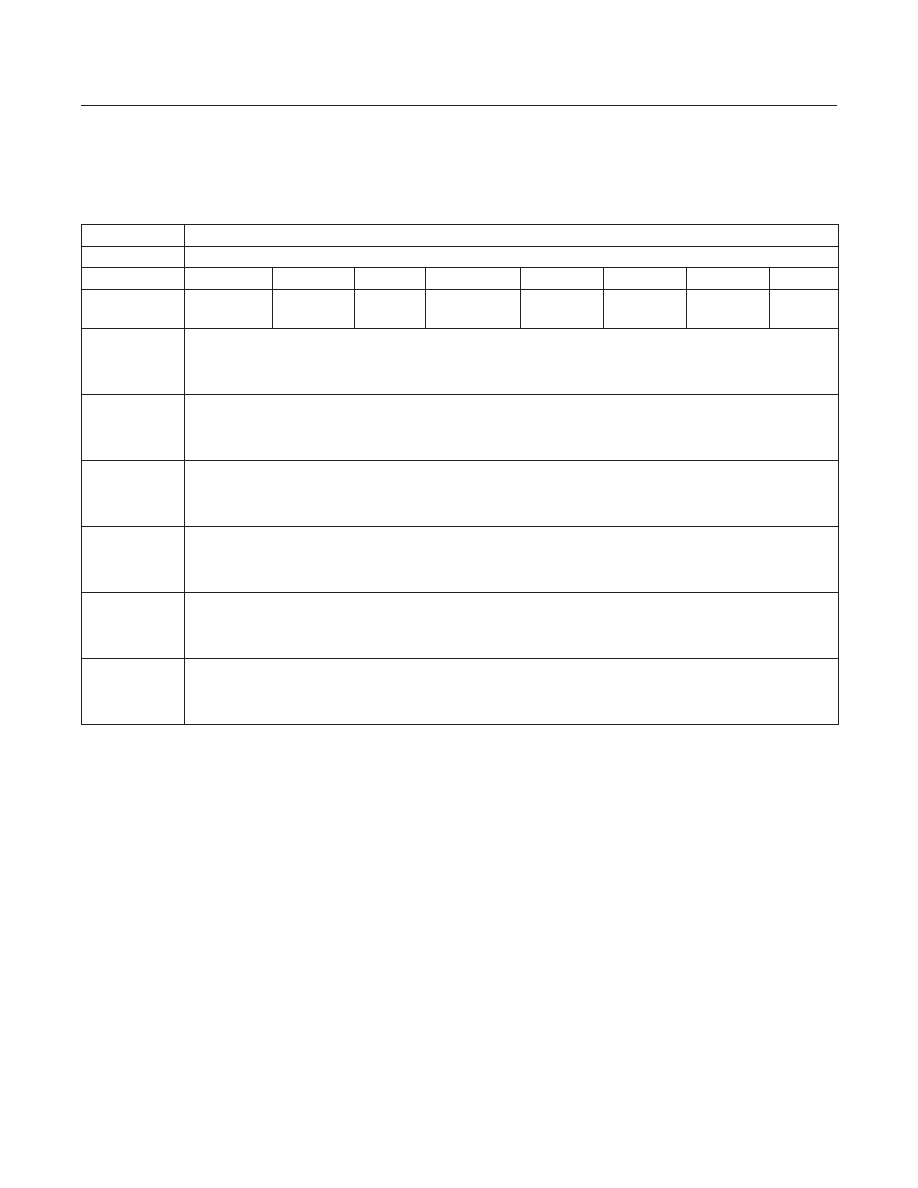

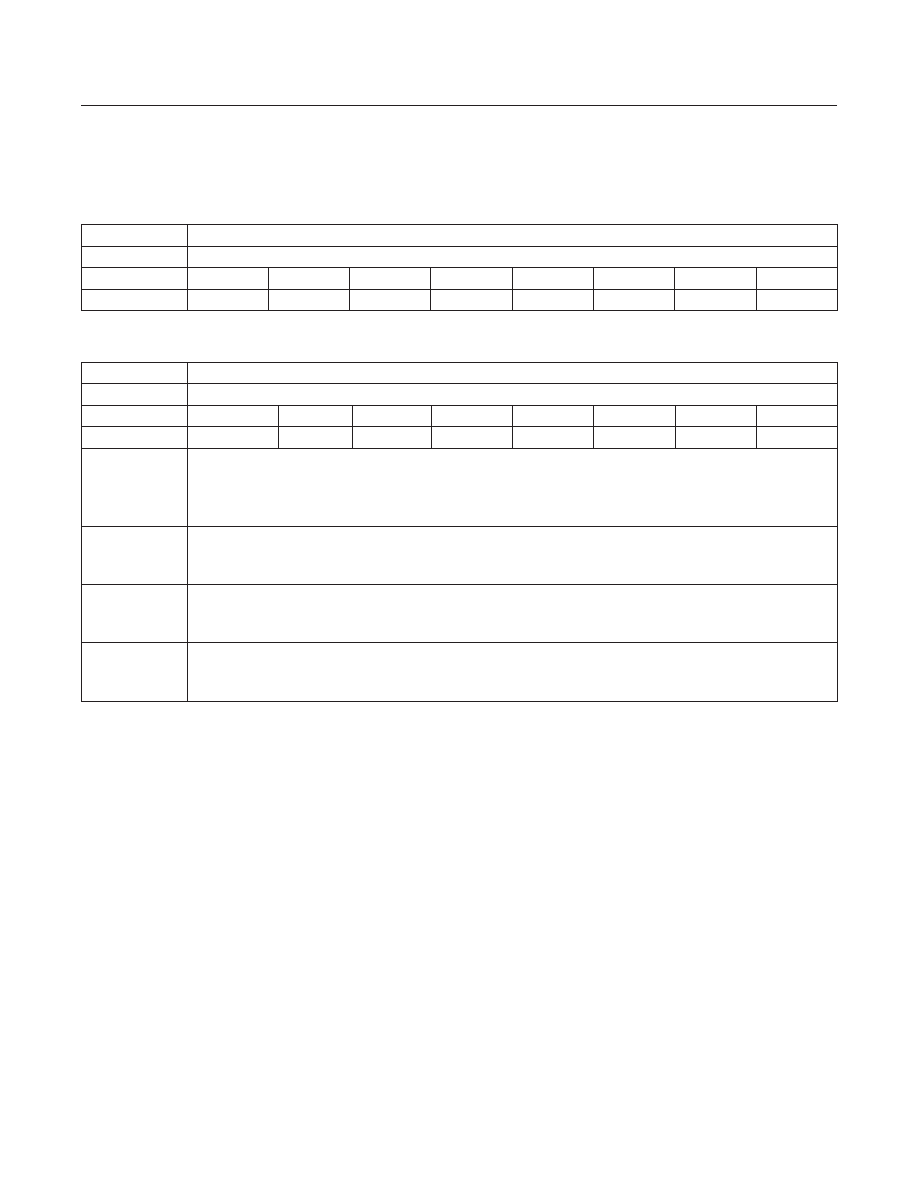

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

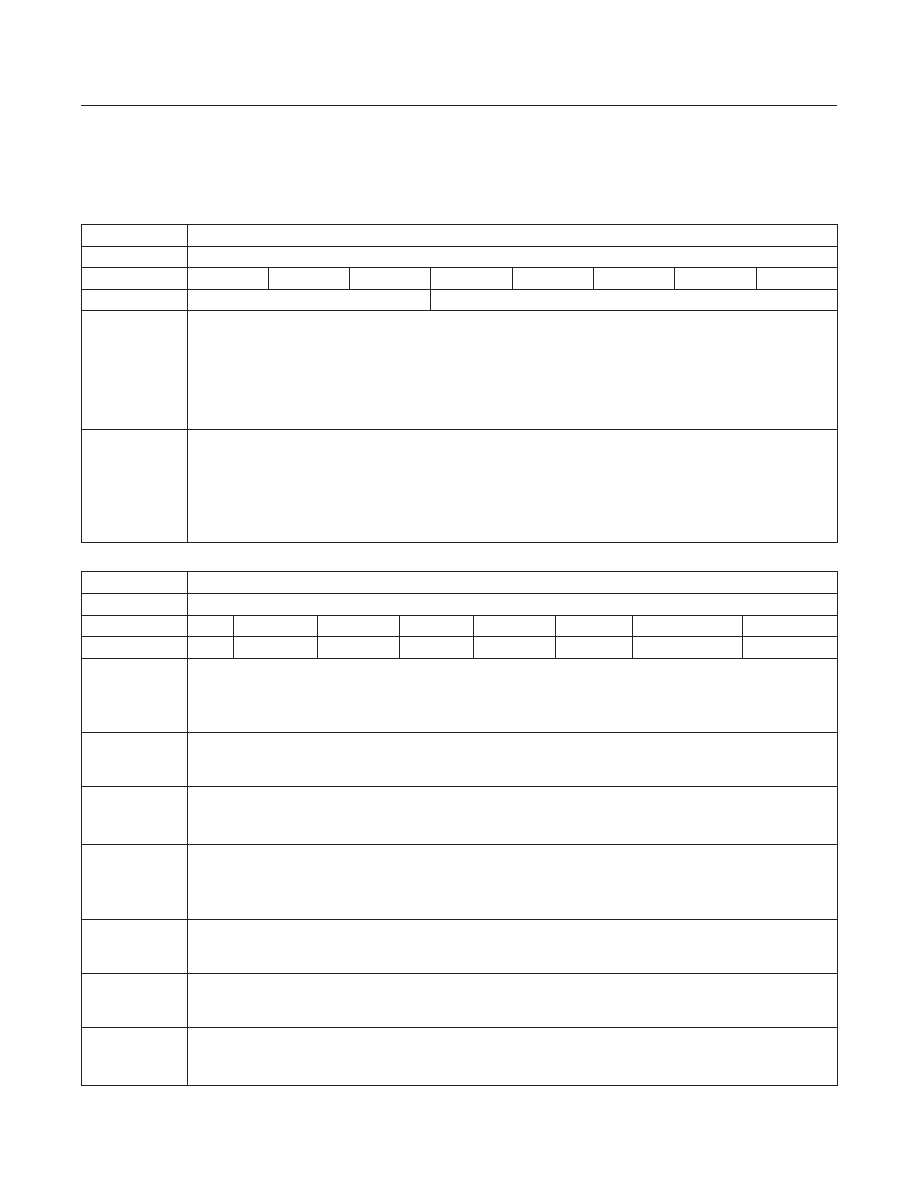

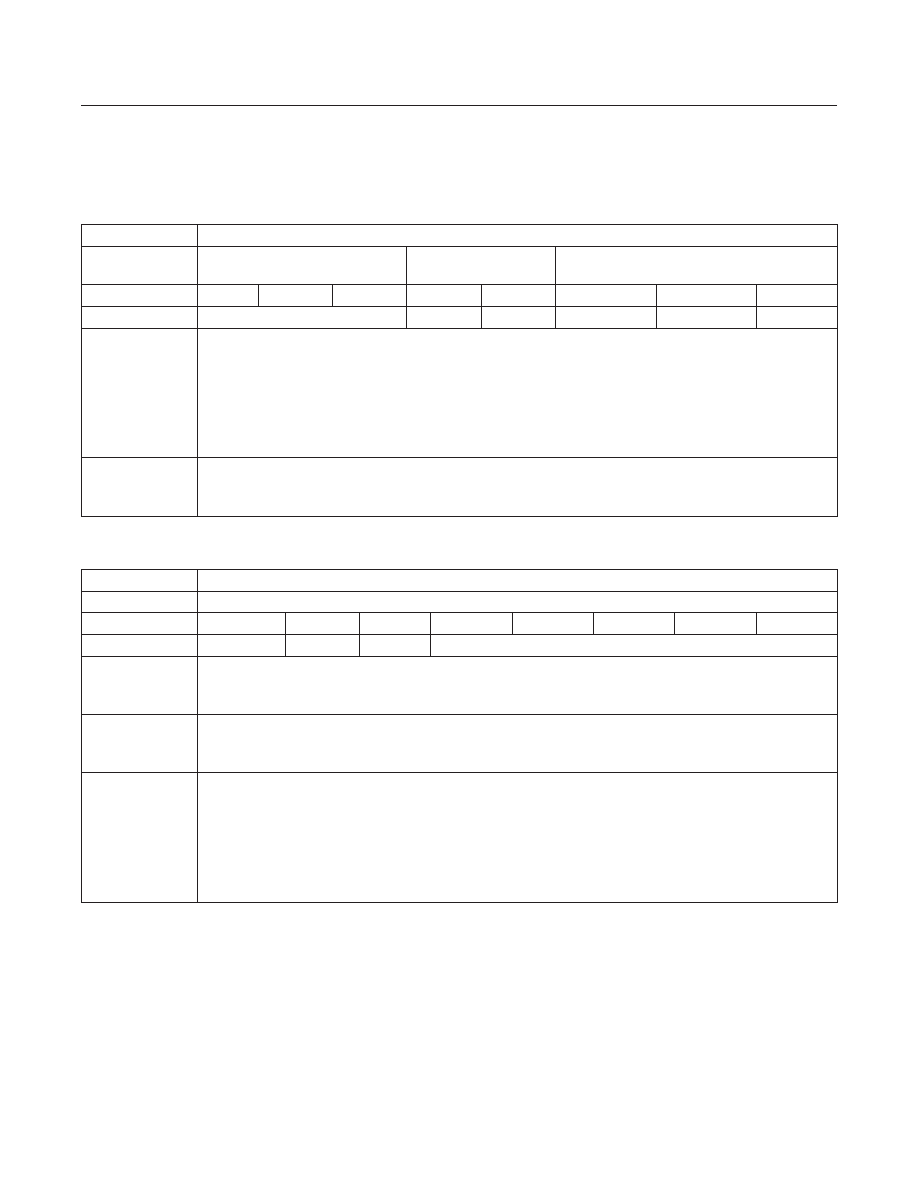

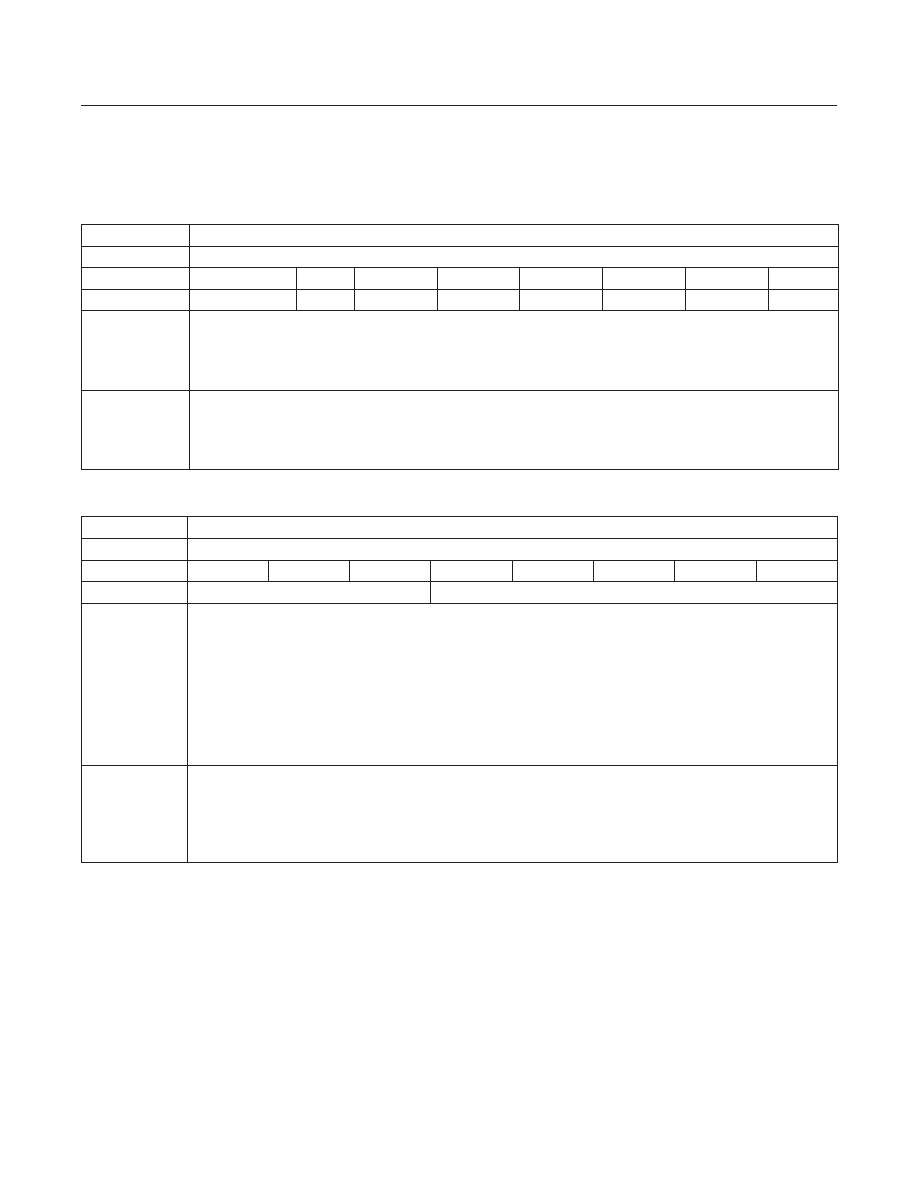

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Current Reduce

Temperature

T

CHG_LIM

120

°C

Thermal Shutdown

Temperature

T

SHUTDOWN

150

°C

Thermal Shutdown

Hysteresis

T

SHUTDOWN_H

20

°C

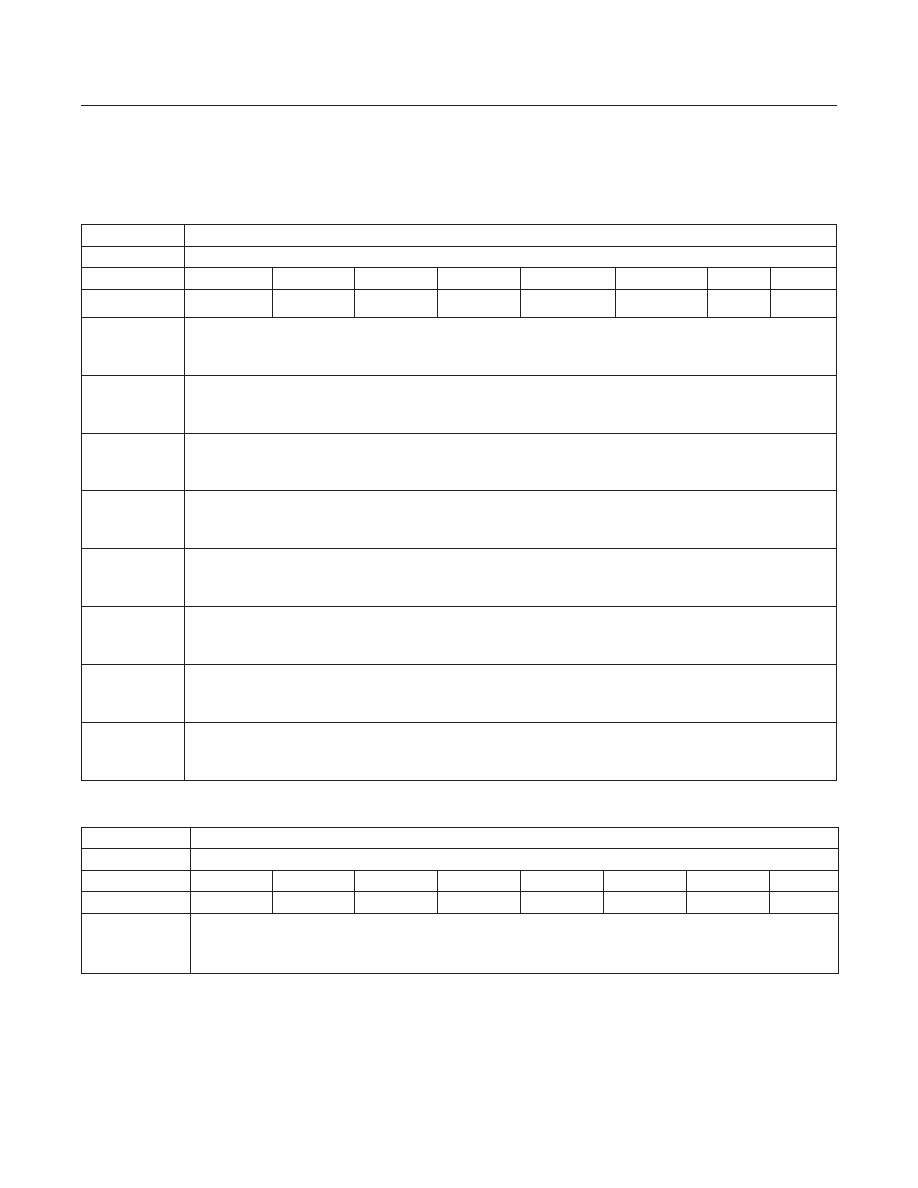

BYP UVLO Threshold

V

BYPUVLO

BYPUVLO[2:0] = 000, V

BYP

falling

3.8

V

BYPUVLO[2:0] = 001, V

BYP

falling

3.9

BYPUVLO[2:0] = 010, V

BYP

falling

4.0

BYPUVLO[2:0] = 011, V

BYP

falling

4.1

BYPUVLO[2:0] = 100, V

BYP

falling

4.2

BYPUVLO[2:0] = 101, V

BYP

falling

4.3

BYPUVLO[2:0] = 110, V

BYP

falling

4.4

BYPUVLO[2:0] = 111, V

BYP

falling

4.5

BYP UVLO Threshold

Hysteresis

V

BYPUVLO_H

25

mV

SYS UVLO (SYSOK)

Threshold

V

SYSUVLO

VPChg[2:0] = 000, V

SYS

rising

5.9

V

VPChg[2:0] = 001, V

SYS

rising

6.0

VPChg[2:0] = 010, V

SYS

rising

6.1

VPChg[2:0] = 011, V

SYS

rising

6.2

VPChg[2:0] = 100, V

SYS

rising

6.3

VPChg[2:0] = 101, V

SYS

rising

6.4

VPChg[2:0] = 110, V

SYS

rising

6.5

VPChg[2:0] = 111, V

SYS

rising

6.6

SYS UVLO Threshold

Hysteresis

V

SYSUVLO_H

500

mV

BYP-SYS BOOST PATH

Switching Frequency

f

BST_SW

0.8

MHz

Maximum Input Current

I

BST_MAX

L = 2.2 µH

3

A

Input Peak Current Limit

I

BST_LIM_PK

4.5

A

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

4

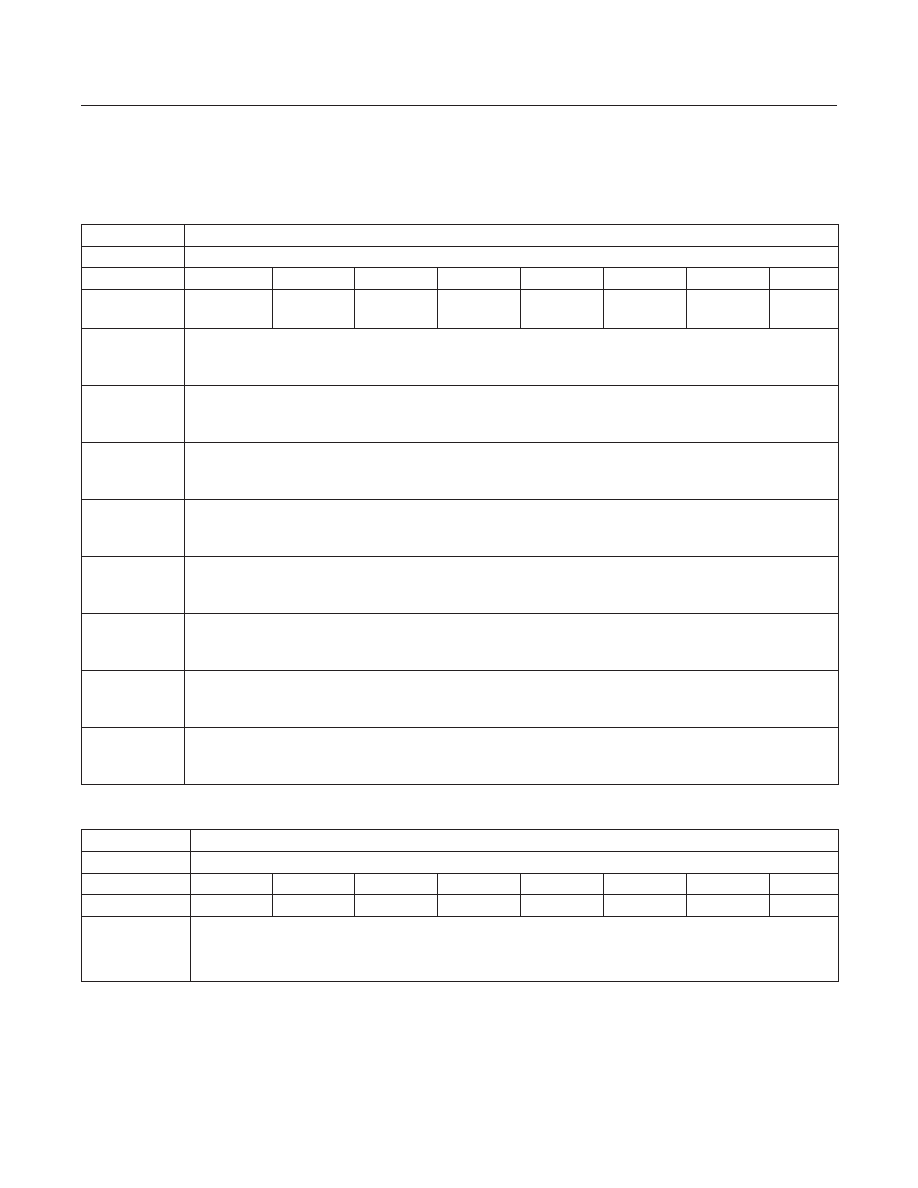

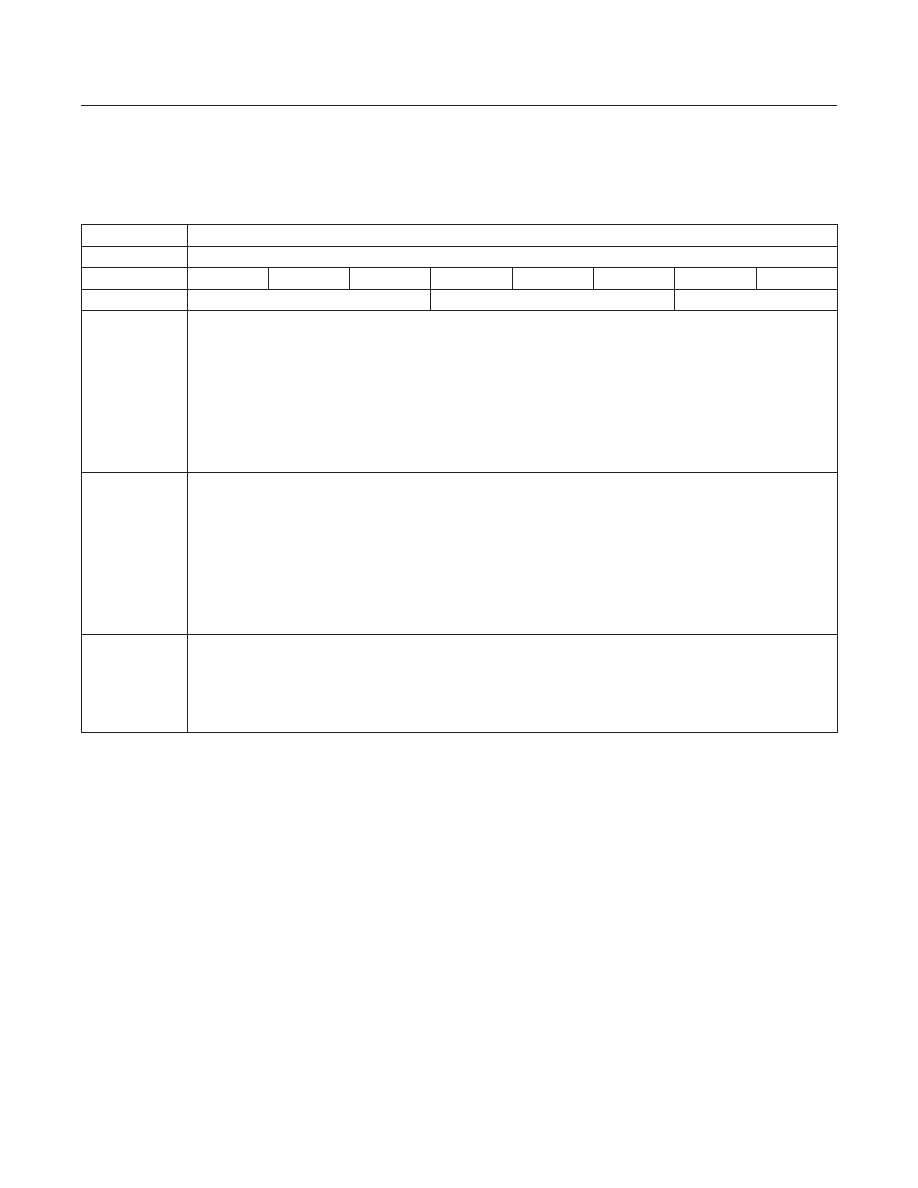

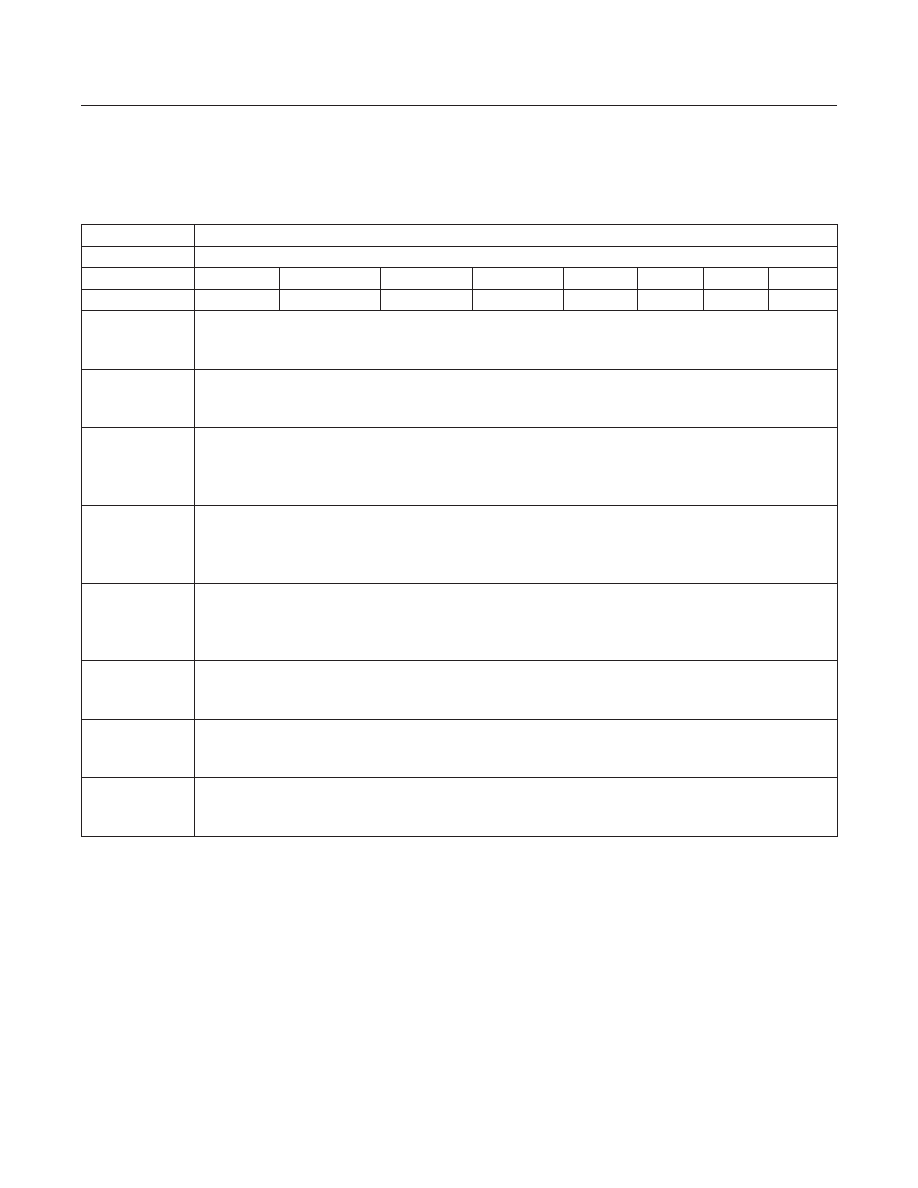

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

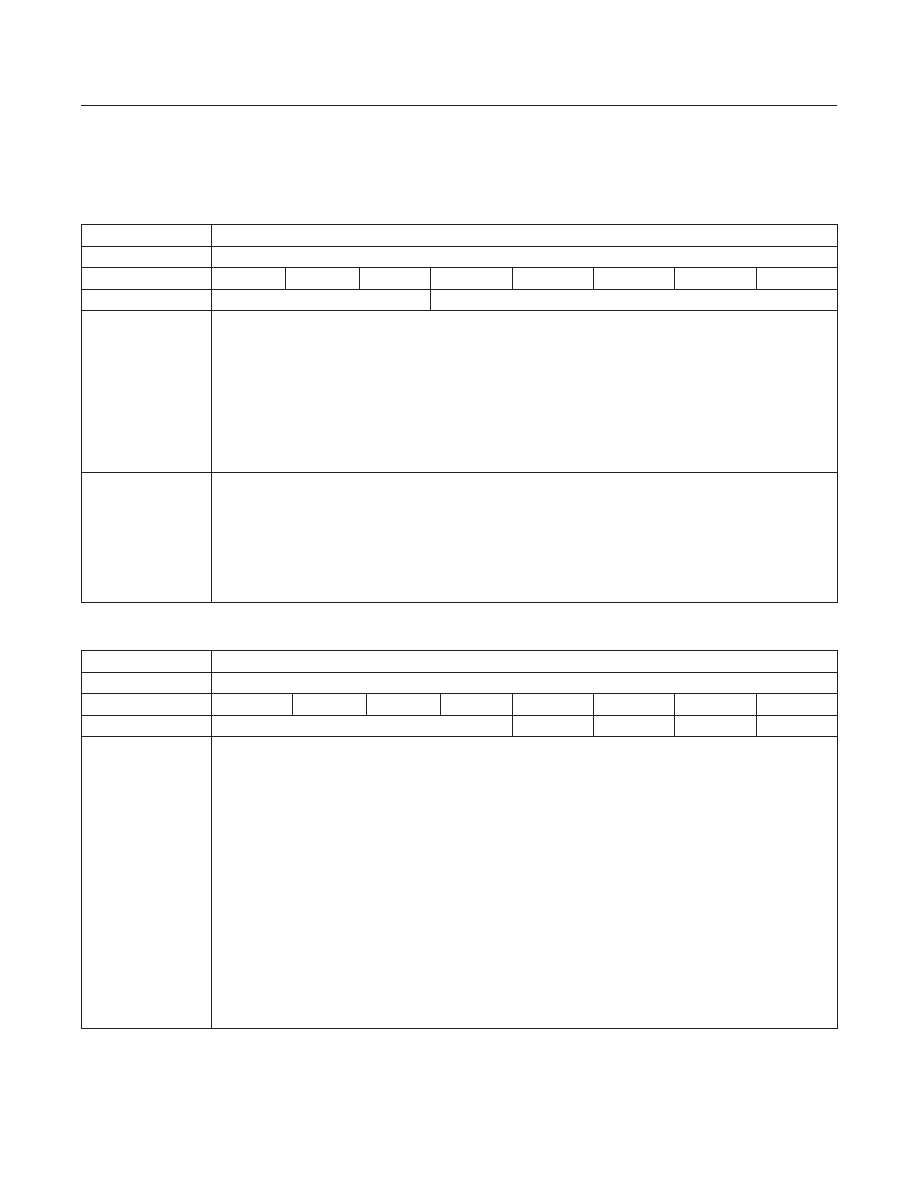

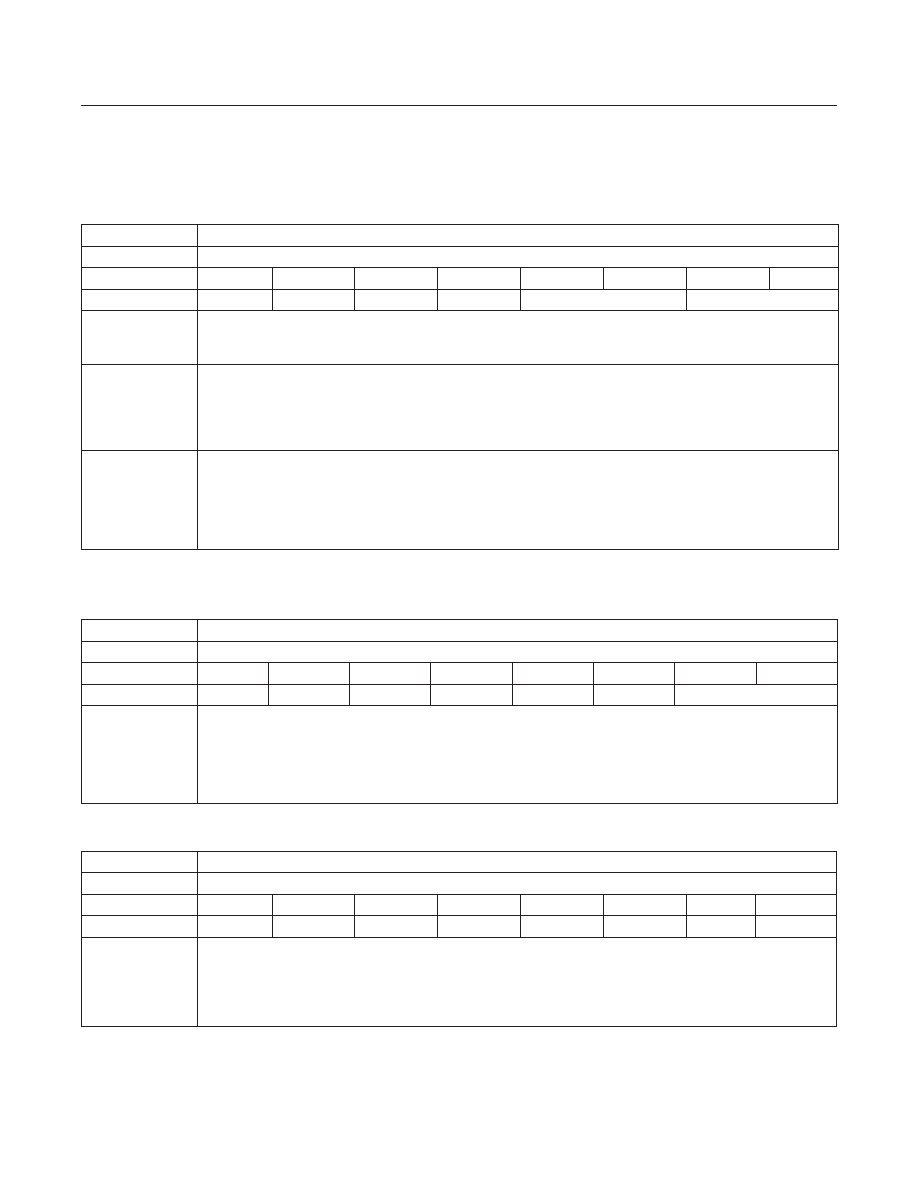

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

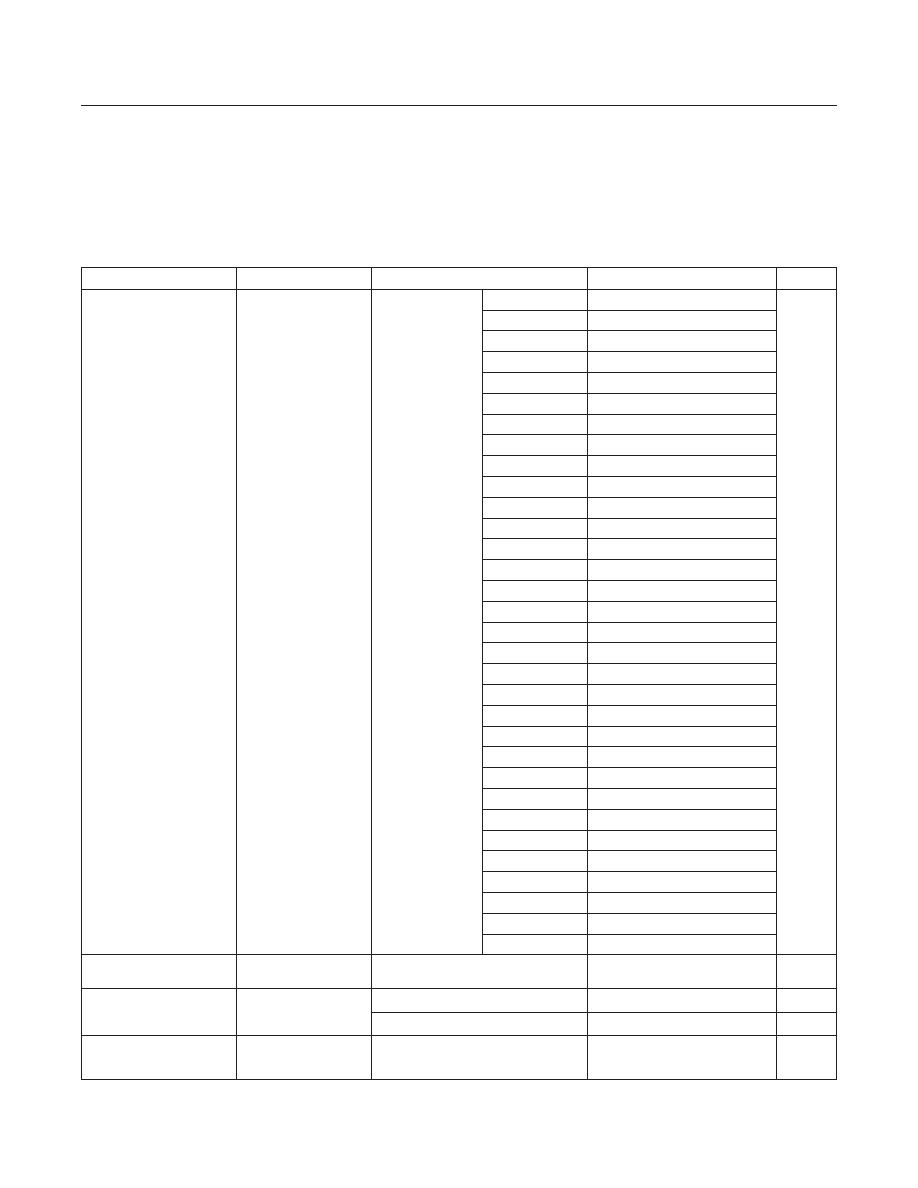

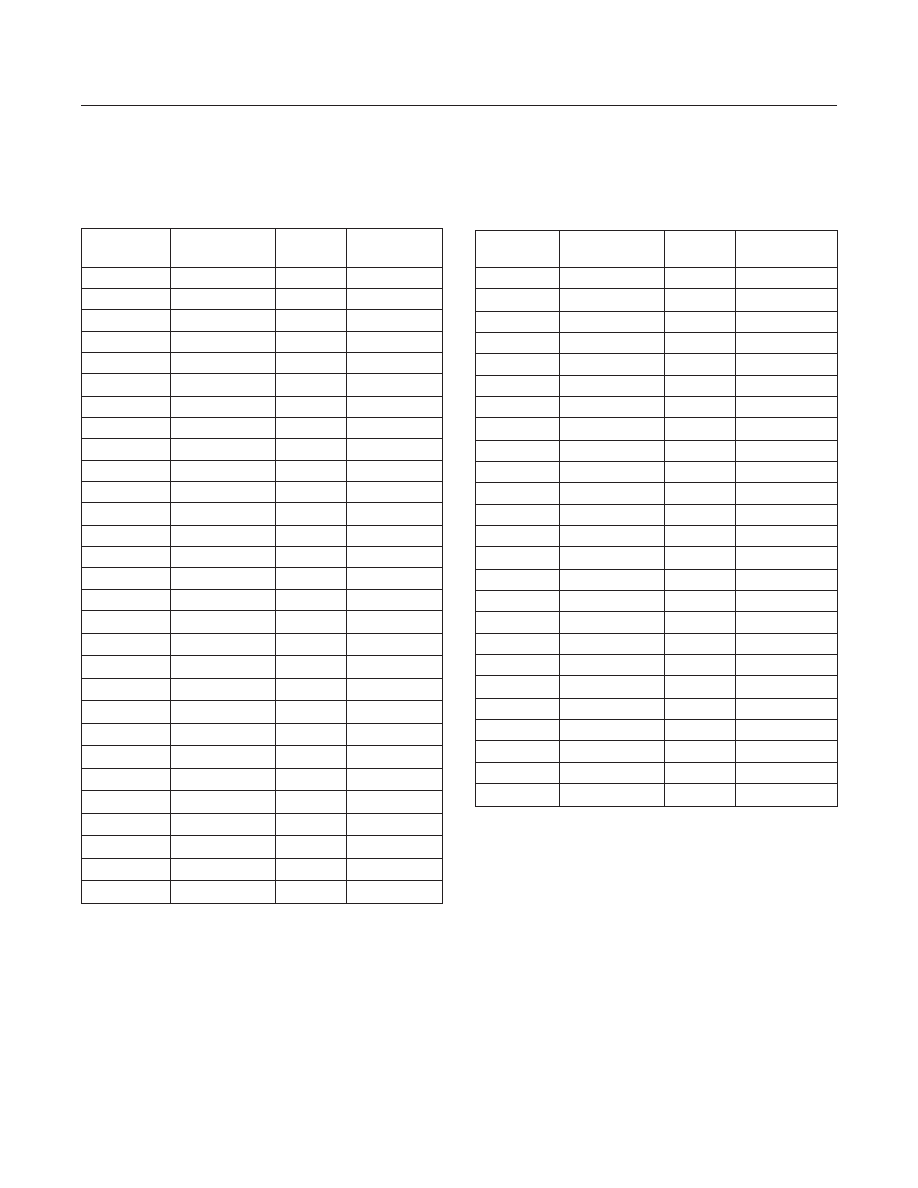

Forced Input Current

Limit

IILIM_F

CurLim1Frc = 1 ,

CurLim1Set[4:0] =

00000

100

mA

00001

200

00010

300

00011

400

00100

405

450

495

00101

600

00110

700

00111

800

01000

900

01001

1000

01010

1100

01011

1200

01100

1300

01101

1400

01110

1500

01111

1600

10000

1700

10001

1800

10010

1900

10011

2000

10100

2100

10101

2200

10110

2300

10111

2400

11000

2500

11001

2600

11010

2700

11011

2800

11100

2900

11101

3000

11110

3100

11111

3200

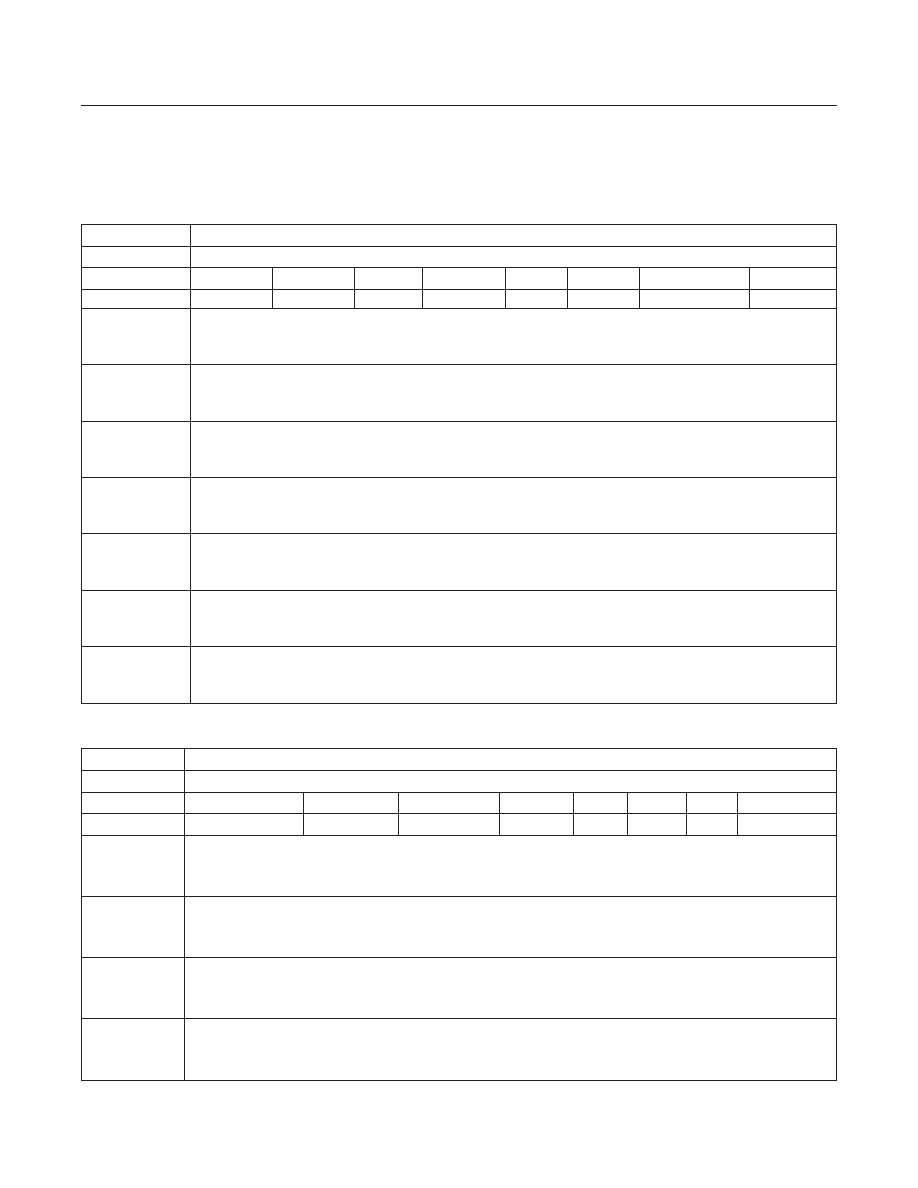

Efficiency

EFF

BST

I

SYS

= 1000mA, V

BAT

= 7.4V,

L1 = Bourns SRP4012TA-2R2M

91.6

%

SYS Regulation Voltage

V

SYS_REG

Charger disabled

V

BAT

+ 0.4

V

Charger in precharge, V

BAT

= 5V

V

PCHG

+ 0.4

V

SYS Regulation Voltage

Limit

V

SYS_LIM

See Battery Charger State

Diagram

V

SYS_REG

- 0.2

V

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

5

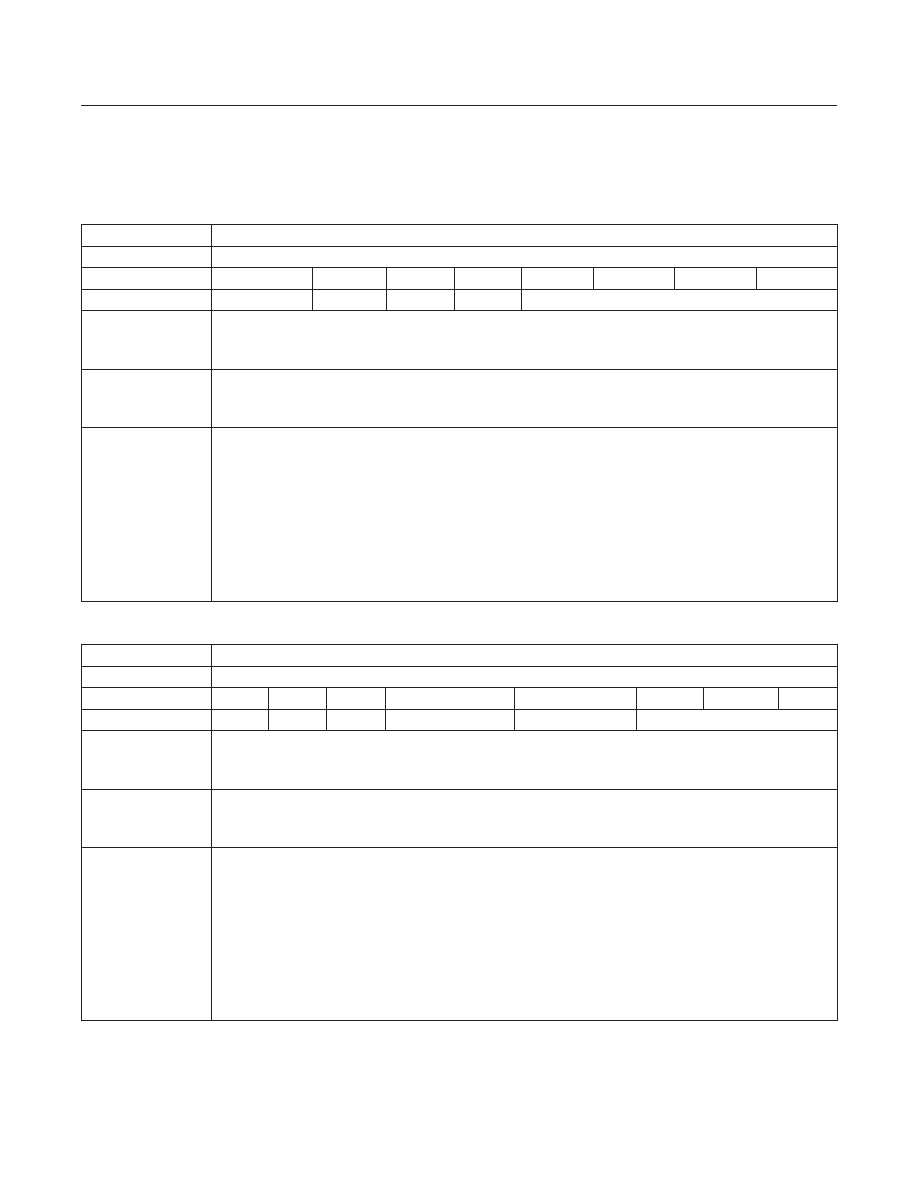

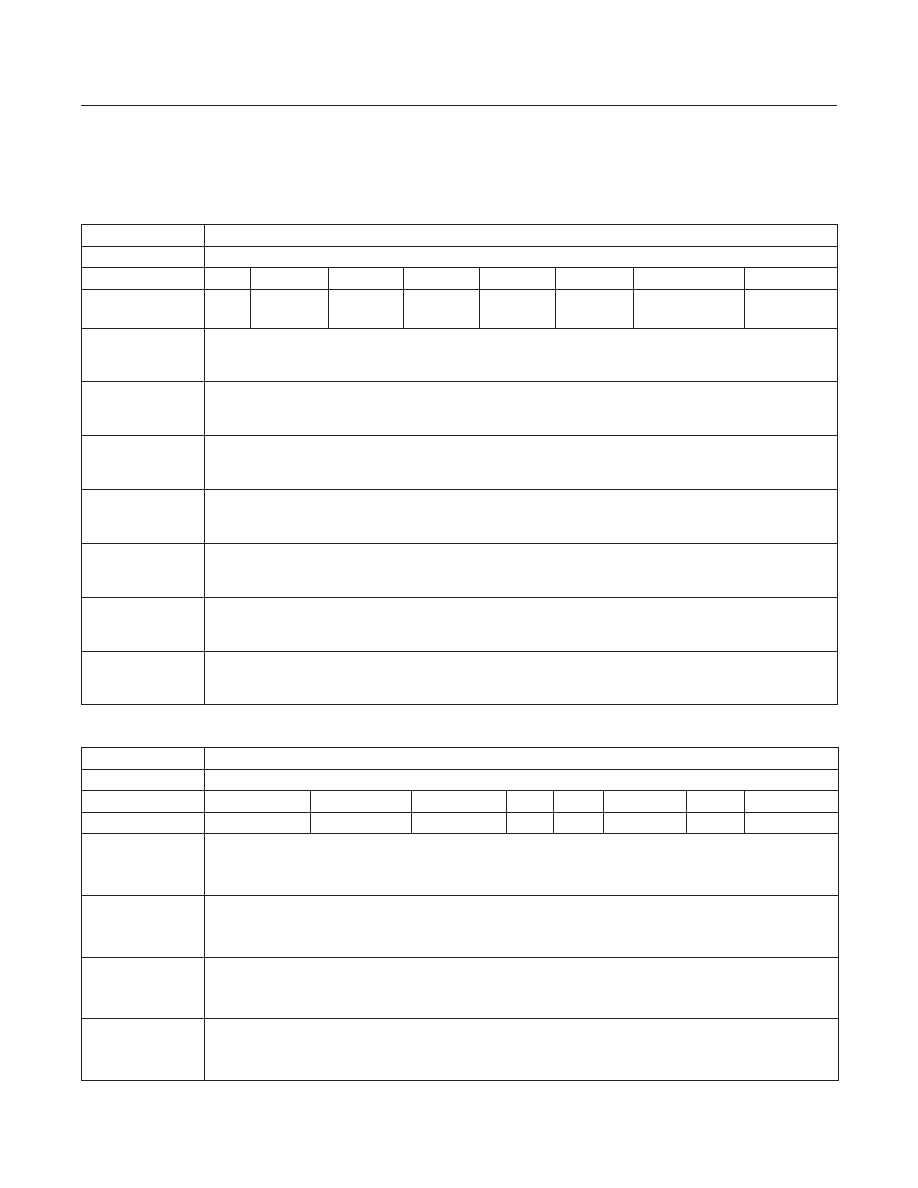

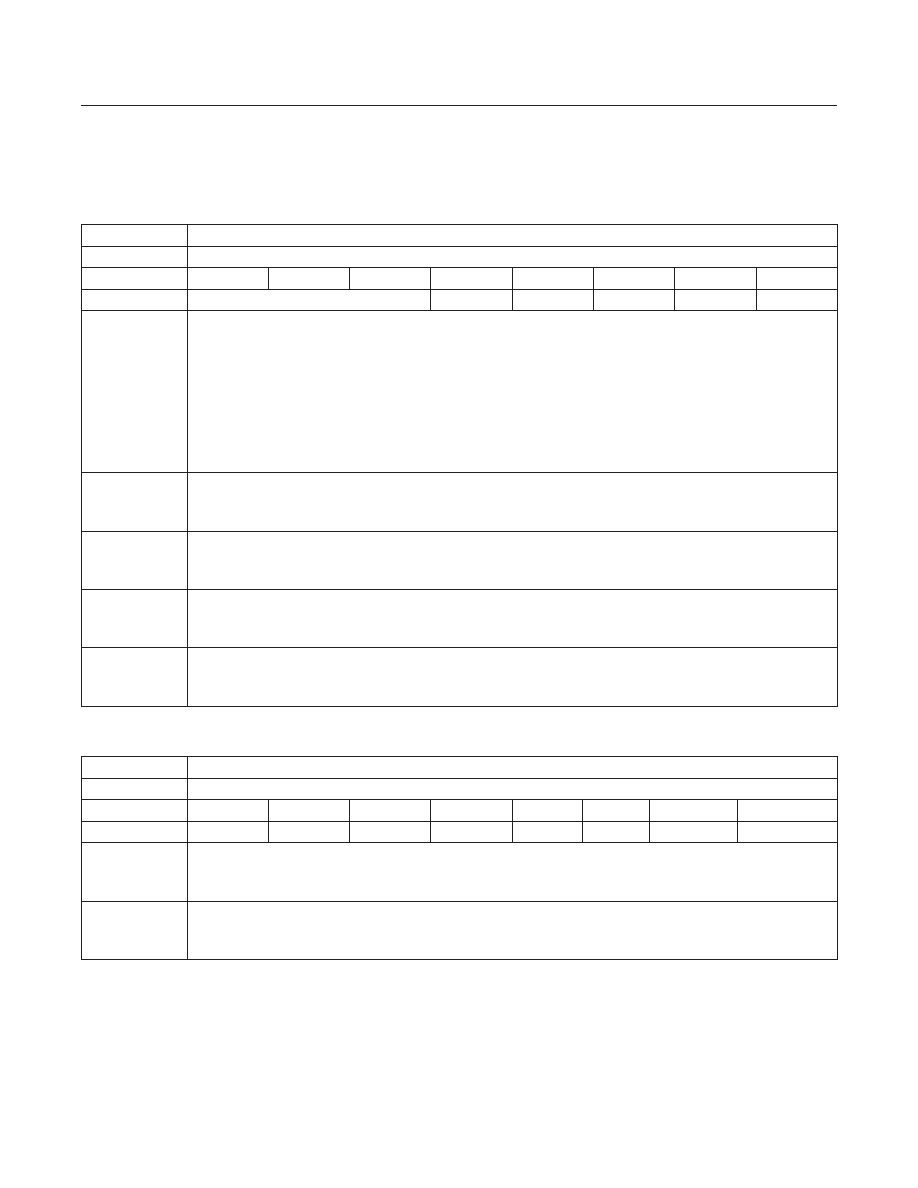

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

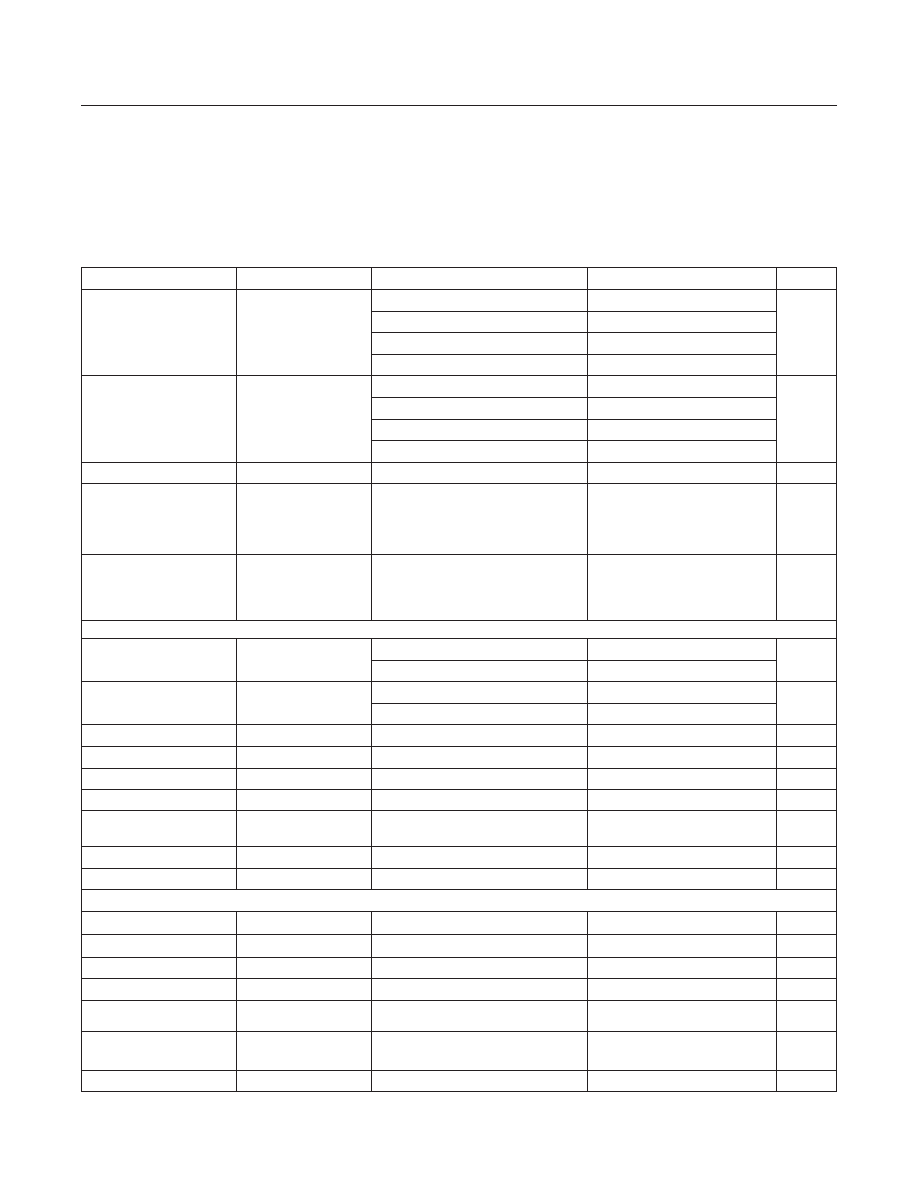

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

BYP-SYS BUCK PATH

Switching Frequency

f

BK_SW

0.8

MHz

Maximum Output

Current

I

BK_MAX

L = 2.2 µH

500

mA

Short-Circuit Peak

Current Limit

I

BK_LIM

1.3

A

Efficiency

EFF

BK

I

CHGIN

= 500mA , V

BAT

= 7.4V,

L1 = Bourns SRP4012TA-2R2M

94

%

Output Voltage Range

V

BK_OUT_RNG

4

5.5

V

Output Accuracy

V

BK_OUT_ACC

-1.5

+1.5

%

SYS-BAT CHARGER/SWITCH CONTROLLER

BAT-to-SYS Regulation

Voltage

V

BAT-SYS_ON

-20

mV

BAT-to-SYS Switch Fast

Turn-On Threshold

V

BAT-SYS_OFF

V

SYS

falling

-100

mV

BAT-to-SYS Switch On-

Resistance

R

BAT_SYS

13

mΩ

Charger Current

Soft-Start Time

t

CHG_SOFT

1

ms

PRECHARGE

Precharge Current

I

PCHG

IPChg[1:0] = 00

5

%I

FCHG

IPChg[1:0] = 01

10

IPChg[1:0] = 10

20

IPChg[1:0] = 11, R

SET

= 20kΩ

27

30

33

Prequalification

Threshold

V

PCHG

VPChg[2:0] = 000

5.7

V

VPChg[2:0] = 001

5.8

VPChg[2:0] = 010

5.9

VPChg[2:0] = 011

6.0

VPChg[2:0] = 100

6.1

VPChg[2:0] = 101

6.2

VPChg[2:0] = 110

6.3

VPChg[2:0] = 111

6.4

Prequalification

Threshold Hysteresis

V

PCHG_H

100

mV

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

6

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

FAST CHARGE

SET Current Gain Factor

K

SET

10000

A/A

SET Regulation Voltage

V

SET

1

V

Fast-Charge Current

I

FCHG

R

SET

= 20kΩ

0.43

0.5

0.57

A

R

SET

= 20kΩ, T = 25 °C

0.475

0.5

0.525

R

SET

= 10kΩ

1

R

SET

= 4kΩ

2.5

Fast-Charge Current

Scaling

I

FCHG_T

T_T_IFChg[2:0] = 000

20

%I

FCHG

T_T_IFChg[2:0] = 001

30

T_T_IFChg[2:0] = 002

40

T_T_IFChg[2:0] = 003

50

T_T_IFChg[2:0] = 004

60

T_T_IFChg[2:0] = 005

70

T_T_IFChg[2:0] = 006

80

T_T_IFChg[2:0] = 007

100

1/2 Fast-Charge Current

Comparator Threshold

I

FC_HALF

50

%I

FCHG

1/5 Fast-Charge Current

Comparator Threshold

I

FC_FIFTH

20

%I

FCHG

MAINTAIN CHARGE

Charge Done

Qualification

I

CHG_DONE

ChgDone[1:0] = 00

5

%I

FCHG

ChgDone[1:0] = 01

10

ChgDone[1:0] = 10, R

SET

= 20kΩ

18

20

22

BAT Regulation Voltage

V

BATREG

BatReg[1:0] = 00, T

A

= +25 °C

8.258

8.3

8.342

V

BatReg[1:0] = 00,

T

A

= -40 °C to +85 °C

8.217

8.3

8.383

BatReg[1:0] = 01

8.4

BatReg[1:0] = 10

8.5

BatReg[1:0] = 11

8.6

BAT Recharge

Threshold

V

BATRECHG

BatReChg[1:0] = 00

200

mV

BatReChg[1:0] = 01

300

BatReChg[1:0] = 10

400

BatReChg[1:0] = 11

500

CHARGE TIMER

Maximum

Prequalification Time

t

PCHG

PChgTmr[1:0] =00

30

min

PChgTmr[1:0] = 01

60

PChgTmr[1:0] = 10

120

PChgTmr[1:0] = 11

240

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

7

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Maximum Fast-Charge

Time

t

FCHG

FChgTmr[1:0] = 00

75

Min

FChgTmr[1:0] = 01

150

FChgTmr[1:0] = 10

300

FChgTmr[1:0] = 11

600

Maintain Charge Time

t

TOCHG

MtChgTmr[1:0] = 00

0

Min

MtChgTmr[1:0] = 01

15

MtChgTmr[1:0] = 10

30

MtChgTmr[1:0] = 11

60

Timer Accuracy

t

ACC

-10

+10

%

Timer Extend Threshold

P

TIMERX

If charge current is reduced due to

I

LIM

or T

DIE

, this is the percentage

of charge current below which

timer clock operates at half speed

50

%

Timer Suspend

Threshold

P

TIMERSUS

If charge current is reduced due to

I

LIM

or T

DIE

, this is the percentage

of charge current below which

timer clock pauses

20

%

THERMISTOR MONITOR AND NTC DETECTION

THM Hot Threshold

T4

V

THM

falling, WarmCoolSel = 0

21.3

23.3

25.3

%V

TPU

V

THM

falling, WarmCoolSel = 1

30.9

32.9

34.9

THM Warm Threshold

T3

V

THM

falling, WarmCoolSel = 0

30.9

32.9

34.9

%V

TPU

V

THM

falling, WarmCoolSel = 1

46.5

50

53.5

THM Cool Threshold

T2

V

THM

rising, WarmCoolSel = 0 or 1

62.5

64.5

66.5

%V

TPU

THM Cold Threshold

T1

V

THM

rising, WarmCoolSel = 0 or 1

71.9

73.9

75.9

%V

TPU

THM Disable Threshold

V

THM_DIS

V

THM

rising

91.0

93.0

95.0

%V

TPU

THM Threshold Hysteresis

V

THM_DIS_H

60

mV

JEITA BAT Voltage

Reduction

V

BAT_JEITA

300

mV

THM Input Leakage

I

THM_LK

-1

+1

µA

THM Detection Time

t

THM_DET

0.35

ms

DIGITAL I/O (SDA, SCL,

FLTIN

, INT, SYSOK, FSUS, LED, CDIR)

Leakage Current

I

IO_LK

-1

+1

µA

Logic Input High-Voltage

V

IO_IH

1.4

V

Logic Input Low-Voltage

V

IO_IL

0.5

V

Logic Output Low-Voltage

V

IO_OL

I

OL

= 4mA

0.4

V

FSUS Input Pulldown

Resistance

R

FSUS_PD

470

kΩ

SDA, SCL Bus Low-

Detection Current

I

PD

V

SDA

= V

SCL

= 0.4V

0.2

0.4

µA

SCL Clock Frequency

f

SCL

Note 3

0

400

kHz

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

8

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Bus Free Time Between

a STOP and START

Condition

t

BUF

1.3

µs

START Condition

(Repeated) Hold Time

t

HD_SDA

Note 3

0.6

µs

Low Period of SCL

Clock

t

LOW

1.3

µs

High Period of SCL

Clock

t

HIGH

0.6

µs

Setup Time for a

Repeated START

Condition

t

SU_STA

0.6

µs

Data Hold Time

t

HD_DAT

Note 4

0

0.9

µs

Data Setup Time

t

SU_DAT

Note 4

100

ns

Setup Time for STOP

Condition

t

SU_STO

0.6

µs

Spike Pulse Widths

Suppressed by Input

Filter

t

SP

Note 5

50

ns

BC1.2 DETECTION

V

DP_SRC

Voltage

V

DP_SRC

/V

SRC06

I

LOAD

= 0 to 200 µA

0.5

0.6

0.7

V

V

DM_SRC

Voltage

V

DM_SRC

/V

SRC06

I

LOAD

= 0 to 200 µA

0.5

0.6

0.7

V

V

D33

Voltage

V

SRC33

I

LOAD

= 0 to 365 µA

2.6

3.4

V

V

DAT_REF

Voltage

V

DAT_REF

0.25

0.32

0.4

V

V

LGC

Voltage

V

LGC

1.5

1.7

1.9

V

I

DM_SINK

Current

I

DM_SINK

/I

DATSINK

0.15V to 3.6V

55

80

105

µA

I

DP_SRC

Current

I

DP_SRC

/I

DCD

0V to 2.5V

7

10

13

μA

R

DM_DWN

Resistor

R

DM_DWN

/R

DWN15

12

20

24

kΩ

I

WEAK

Current

I

WEAK

0.01

0.1

0.5

µA

V

BUS31

Threshold

V

BUS31

DP and DN pins. Threshold in

percent of V

BUS

voltage

4V < V

BUS

< 5.5V

26

31

36

%

V

BUS47

Threshold

V

BUS47

DP and DN pins. Threshold in

percent of V

BUS

voltage

4V < V

BUS

< 5.5V

43.3

47

51.7

%

V

BUS64

Threshold

V

BUS64

DP and DN pins. Threshold in

percent of V

BUS

voltage

4V < V

BUS

< 5.5V

57

64

71

%

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

9

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Charger Detection Debounce

t

CDDEB

45

50

55

ms

Primary-to-Secondary Timer

t

PDSDWAIT

27

35

39

ms

Proprietary Charger

Debounce

t

PRDEB

5

7.5

10

ms

Data Contact Detect

Timeout

t

DCDTMO

DCD2s = 0

700

800

900

ms

DCD2s = 1

1.8

2.0

2.2

DP/DN Overvoltage

Debounce

t

OVDXDEB

90

100

110

µs

OVDX Comparator

OVDX

THRESHOLD

Rising

0

0.15

V

Falling

-0.04

+0.08

CDP/CDN Pulldown

Resistor

R

CDP/CDN_PD

3

6

12

mΩ

TYPE-C DETECTION

V

CONN

Switch Voltage Drop

V

CONN_REQ

V

CONN

= 5.5V, I

CC_LOAD

= 20mA

5.5

5.6

V

V

CONN

Bulk Capacitance

C

VCONN

10

220

µF

CC Pin Operational

Voltage Range

V

CONN_RNG

5.5

V

CC Pin Voltage in DFP

3.0A Mode

V

CC_PIN30

3.1

V

CC Pin Voltage in DFP

1.5A Mode

V

CC_PIN15

1.85

V

CC Pin Low-Power Mode

Pulldown Resistance

R

LPPD_CC_

170

kΩ

CC Pin Low-Power Mode

Voltage Threshold

V

LP_CC_

Rising

0.7

V

CC Pin Clamp Requirements

V

CC_PIN_CLAMP

60 µA ≤ I

CC_

≤ 600 µA

1.1

1.32

V

CC UFP Pulldown Resistance

R

DUFP_CC_

4.59

5.1

5.61

kΩ

CC DFP 0.5A Current

Source

I

DFP0.5_CC_

72

80

88

µA

CC DFP 1.5A Current

Source

I

DFP1.5_CC_

165.6

180

194.4

µA

CC DFP 3.0A Current

Source

I

DFP3.0_CC_

303.6

330

356.4

µA

CC R

A

and R

D

Threshold

V

RA_RD0.5

Rising

0.16

0.2

0.25

V

Falling

0.15

CC UFP 0.5A R

D

Threshold

V

UFP_RD0.5

Rising

0.62

0.66

0.7

V

Falling

0.61

CC UFP 1.5A R

D

Threshold

V

UFP_RD1.5

Rising

1.17

1.23

1.31

V

Falling

1.16

CC V

CONN

Detect

Threshold

V

VCONN_DET

Rising

2.11

2.25

2.4

V

Falling

2.1

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

10

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CC DFP V

OPEN

Detect

Threshold

V

DFP_VOPEN

Rising

1.51

1.575

1.65

V

Falling

1.5

CC DFP V

OPEN

with

3.0A Detect Threshold

V

DFP_VOPEN3A

Rising

2.46

2.6

2.75

V

Falling

2.45

V

V

BUS

Valid

V

BDET

Rising

3.8

4.12

4.4

V

V

BUS

Valid Hysteresis

V

BDET_H

Falling hysteresis

0.7

V

V

BUS

Discharge Value

V

SAFE0V

Falling. Voltage level where a

connected UFP will find V

BUS

removed.

0.6

0.7

0.84

V

Rising hysteresis

100

mV

CC Pin Power-Up Time

t

CLAMPSWAP

The maximum time allowed from

removal of voltage clamp to

attachment of the 5.1k resistor

15

ms

Type-C CC Pin

Detection Debounce

t

CCDEB

100

200

ms

Type-C Debounce

t

PDDEB

10

20

ms

Type-C Quick Debounce

t

QDEB

0.9

1

1.9

ms

V

BUS

Debounce

t

VBDEB

9

10

11

ms

V

SAFE0V

Debounce

t

VSAFE0VDEB

9

10

11

ms

Type-C Error Recovery

Delay

t

ERRORRECOVERY

25

ms

Type-C DRP Toggle

Time

t

DRP

50

100

ms

Duty Cycle of DRP

Swap

D

DRP

Duty cycle of UFP to DFP role

swap

30

70

%

DRP Transition Time

t

DRPTRAN

Time a role swap from DFP to UFP

or reverse is completed

1

ms

DRP Lock Time

t

DRPLOCK

DRP Lock wait time before

transition to unattached state

100

150

ms

V

CONN

Enable Time

t

VCONNON

Time from when V

BUS

is supplied

in DFP mode in state Attach.DFP.

DRPWait

10

ms

V

CONN

Disable Time

t

VCONNOFF

Time from UFP detached or as

directed by I

2

C command until

V

CONN

is removed

35

ms

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

11

Electrical Characteristics (continued)

(V

BAT

= 8.3V, T

A

= -40 °C to +85 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

Note 2: All devices are 100% production tested at T

A

= +25 °C. Limits over the operating temperature range are guaranteed by

design and characterization.

Note 3: f

SCL

must meet the minimum clock low time plus the rise/fall times.

Note 4: The maximum t

HD:DAT

has to be met only if the device does not stretch the low period (t

LOW

) of the SCL signal.

Note 5: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CC Pin Current Change

Time

t

SINKADJ

Time from CC pin changes state in

UFP mode until current drawn from

DFP reaches new value

60

ms

V

BUS

On-Time

t

VBUSON

Time from UFP is attached until

V

BUS

On

275

ms

V

BUS

Off-Time

t

VBUSOFF

Time from UFP is detached until

V

BUS

reaches V

SAFE0V

650

ms

BVCEN Output Low-

Voltage

V

BVCEN_OL

I

SINK

= 1mA

0.4

V

BVCEN Output High-

Voltage

V

BVCEN_OH

I

SOURCE

= 1mA

V

CCINT

- 0.4

V

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

12

Electrical Characteristics (continued)

(V

BAT

= 8.5V, T

A

= -20 °C to +70 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

MAX14748

USB Type-C Charger

Maxim Integrated

13

www.maximintegrated.com

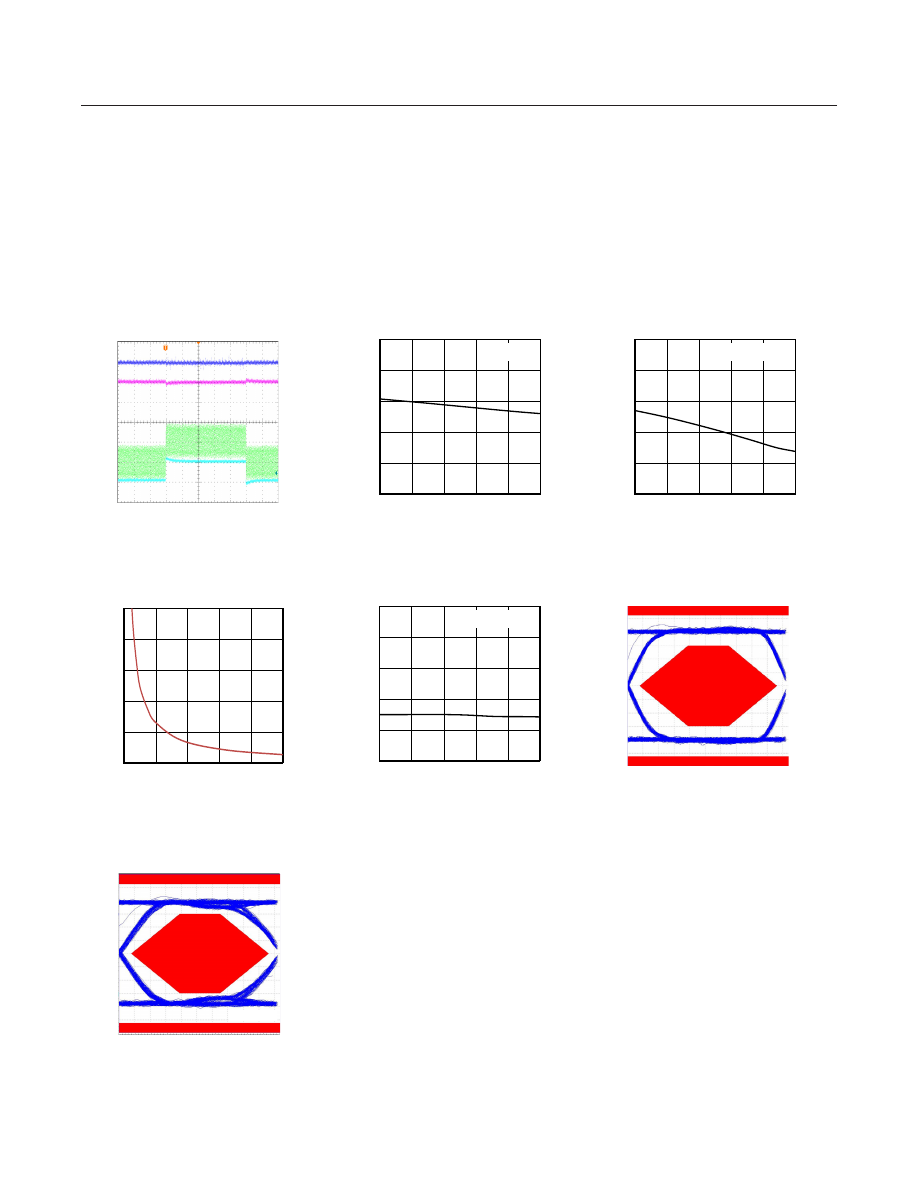

Typical Operating Characteristics

7

7.2

7.4

7.6

7.8

8

0

800

1600

2400

3200

V

SYS

(V

)

I

CHGIN

(mA)

V

SYS

vs. I

CHGIN

toc04

V

BAT

= 7.4V

SpvChgILim[4:0] = 11101

SpvChgILim[4:0] = 01110

SpvChgILim[4:0] = 00100

4.9

4.94

4.98

5.02

5.06

5.1

0

100

200

300

400

500

V

CHG

IN

(V

)

I

CHGIN

(mA)

BUCK OUTPUT LOAD REGULATION

toc05

V

BAT

= 7.4V

50

60

70

80

90

100

0

300

600

900

1200

1500

EF

FI

CI

ENCY

(%

)

I

SYS

(mA)

BOOST EFFICIENCY vs. LOAD

toc06

V

BAT

= 6.0V

V

BAT

= 8.6V

V

BAT

= 7.4V

INPUT: CHGIN

OUTPUT: SYS

L1 = BOURNS SRP4012TA-2R2M

0

40

80

120

160

200

6

7

8

9

BA

TT

ER

Y I

NP

UT

CURRE

NT

I

BA

T

( µ

A)

BATTERY VOLTAGE V

BAT

(V)

I

BAT

vs. V

BAT

toc01

LOW POWER MODE,

CHGIN FLOATING

TYPE-C ADAPTER

ATTACHED

NOT LOW POWER

MODE, CHGIN FLOATING

ChgEn =0

0

0.4

0.8

1.2

1.6

2

0

2

4

6

8

10

0.00

50.00

100.00

150.00

200.00

250.00

BA

TT

ER

Y CURRE

NT

(A

)

BA

TT

ER

Y VO

LT

AG

E (

V)

TIME (MINUTE)

I

BAT

and V

BAT

vs. TIME

toc02

2200mAH BATTERY

ChgDone[1:0] = 00

IPChg[1:0] = 00

VPChg[2:0] = 001

R

SET

= 10k

W

VOLTAGE

CURRENT

6.5

6.9

7.3

7.7

8.1

8.5

0

500

1000

1500

2000

V

SYS

(V

)

I

SYS

(mA)

V

SYS

vs. I

SYS

toc03

V

BAT

= 7.4V

SpvChgILim[4:0] = 11101

SpvChgILim[4:0] = 01110

SpvChgILim[4:0] = 00100

50

60

70

80

90

100

0

100

200

300

400

500

EF

FI

CI

ENCY

(%

)

I

CHGIN

(mA)

REVERSE BUCK

EFFICIENCY vs. LOAD

toc07

BBFrxZX = 0

INPUT: BAT

OUTPUT: CHGIN

L1 = BOURNS SRP4012TA-2R2M

BBFrxZX = 1

toc08

2ms/div

BOOST TRANSIENT RESPONSE

V

SYS

1V/div

I

SYS

500mA/div

V

BAT

= 7.4V,

ChgEn = 0

500mA/div

toc09

200

ms/div

BUCK TRANSIENT RESPONSE

(BBFrxZX = 1)

V

SYS

1V/div

I

CHGIN

V

CHGIN

I

INDUCTOR

500mA/div

1V/div

(V

BAT

= 8.5V, T

A

= -20 °C to +70 °C, all registers in their default state, unless otherwise noted. Typical values are at V

CHGIN

= 5.0V,

V

BAT

=7.4V, V

SYS

= V

BATREG

, T

A

= +25 °C.)

MAX14748

USB Type-C Charger

Maxim Integrated

14

www.maximintegrated.com

Typical Operating Characteristics (continued)

0

400

800

1200

1600

2000

0

20

40

60

80

100

B

A

T

T

E

R

Y

CURRE

NT

(

m

A

)

R

SET

(k

W)

FAST CHARGE CONSTANT

CURRENT vs. R

SET

toc13

500mA/div

toc10

200

ms/div

BUCK TRANSIENT RESPONSE

(BBFrxZX = 0)

V

SYS

1V/div

I

CHGIN

V

CHGIN

I

INDUCTOR

500mA/div

1V/div

toc16

TIME (0.2ns/div)

EYE DIAGRAM

(WITH DEVICE PRESENT)

U

SB D

IF

FER

EN

TI

AL

SI

G

N

AL

(V)

0.1V/div

V

L3OUT

= 3.0V

I

SYS

= 300mA

40

44

48

52

56

60

-40

-15

10

35

60

85

CHA

RG

ING

CURRE

NT

I

BA

T

(mA

)

TEMPERATURE ( °C)

PRECHARGE CURRENT vs.

TEMPERATURE

toc11

R

SET

= 10k

W

IPChg[1:0] = 00

900

940

980

1020

1060

1100

-40

-15

10

35

60

85

CHA

RG

ING

CURRE

NT

I

BA

T

(mA

)

TEMPERATURE ( °C)

FAST CHARGE CONSTANT

CURRENT vs. TEMPERATURE

toc12

R

SET

= 10k

W

8

8.2

8.4

8.6

8.8

9

-40

-15

10

35

60

85

BA

TT

ER

Y R

EG

U

LA

TI

O

N

VO

LT

AG

E (

V)

TEMPERATURE ( °C)

BATTERY REGULATION

VOLTAGE vs. TEMPERATURE

toc14

R

SET

= 10k

W

toc15

TIME (2ns/div)

EYE DIAGRAM

(WITHOUT DEVICE PRESENT)

U

SB D

IF

FER

EN

TI

AL

SI

G

N

AL

(V)

0.1V/div

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

15

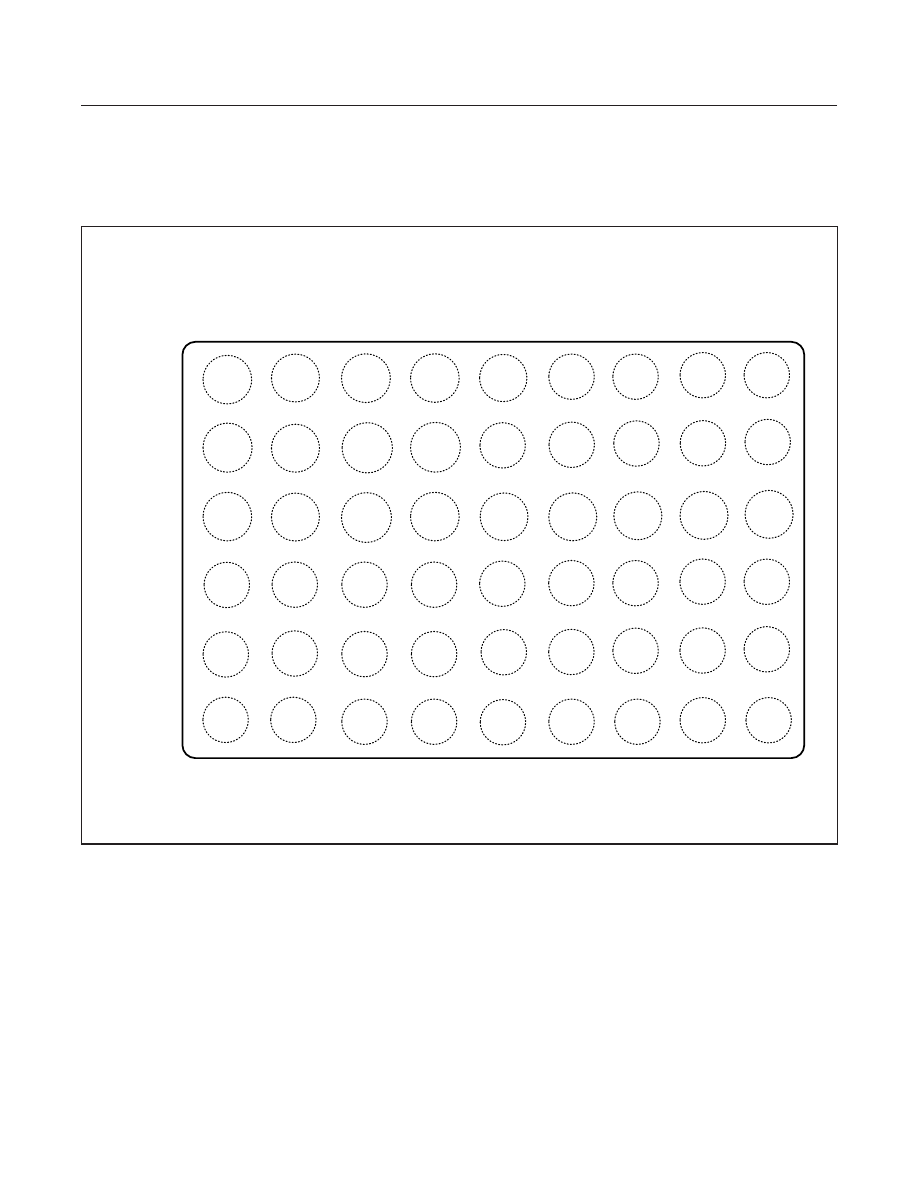

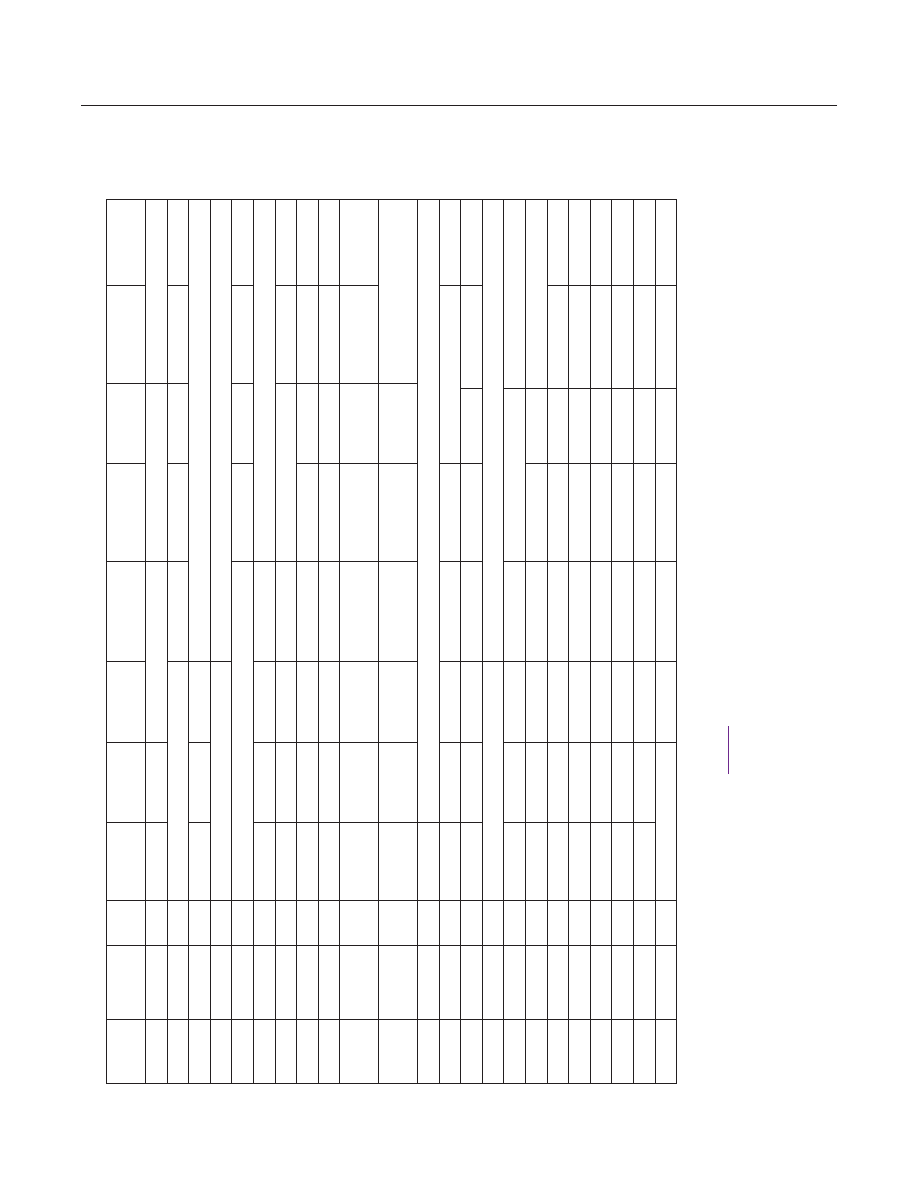

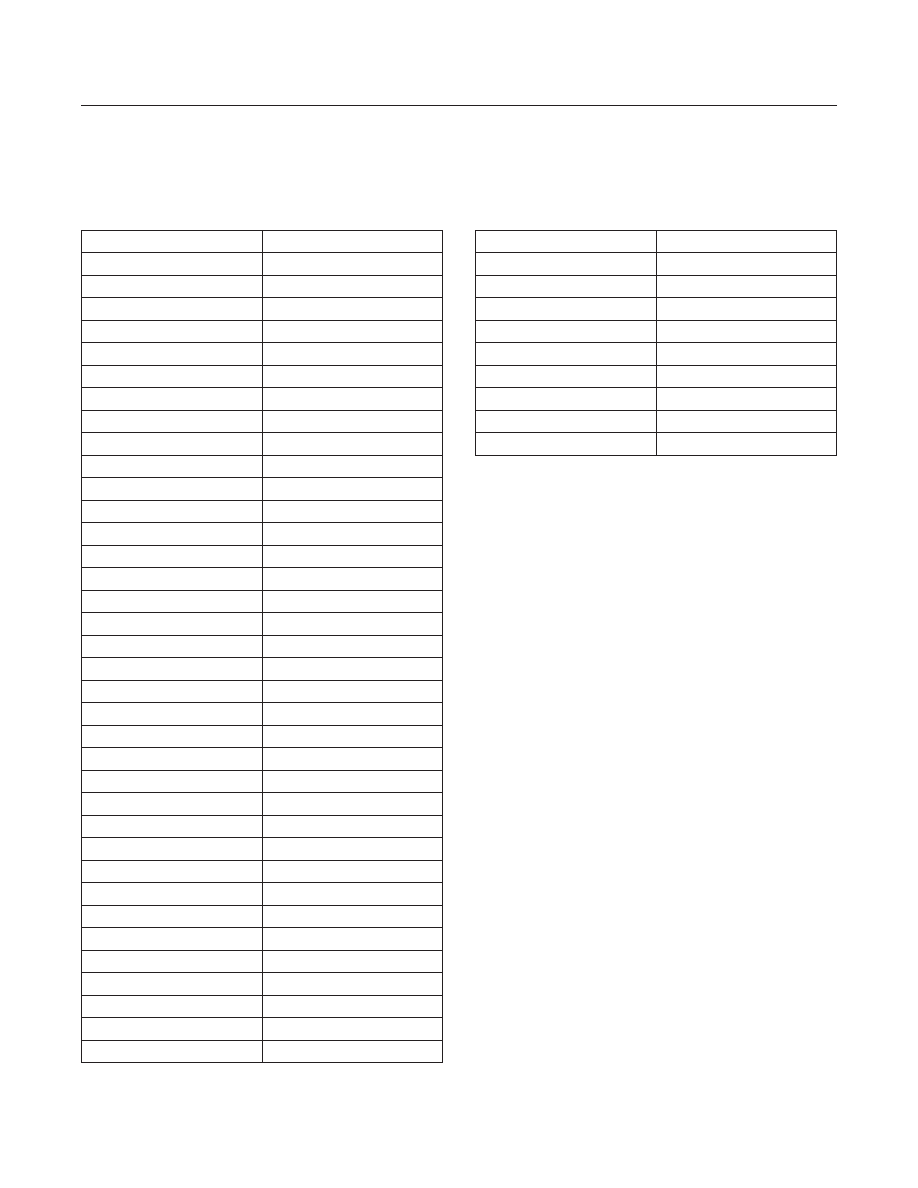

Bump Configurations

1

2

3

4

A

B

C

D

GND

THM

VTPU

GND

BREG

FSUS

E

5

SYSOK

NVP

SDA

LED

GND

CC1

SCL

CC2

CDN

6

FLINT

COMP

CHGIN

GND

F

CDIR

CDP

TDP

CHGIN

INT

VCONN

BST

TPU

DGND

TDN

SYS

SET

BYP

PGND

LX

SYS

BAT

BYP

PGND

LX

7

CHGIN

CHGIN

SYS

BAT

BYP

PGND

LX

SYS

BAT

BYP

PGND

LX

8

9

TOP VIEW

(BUMP SIDE DOWN)

MAX14748

WLP

3.968mm x 2.768mm

VCCINT

SFOUT

BVCEN

BUMP

NAME

FUNCTION

A1

AGND

Analog Ground.

A2

FLTIN

Charger Fault Input. Logic-low on this pin forces the charger into a fault state and generates an

interrupt. See Register 0x35 description for more information. Connect to digital I/O supply if not used.

A3

SYSOK

Open-Drain Status Output of SYS Regulation. When V

SYS

is above the SYS UVLO threshold and Boost

is active, this output is high-impedance. When V

SYS

is below the SYS UVLO threshold, this output is

low. Leave unconnected if not used.

A4

TPU

High-Side of Internal Resistor for THM Detection. Connect a 10k resistor between this pin and THM.

A5

COMP

Buck/Boost Converter Compensation Connection. Connect a 3.9nF capacitor for internal Buck/Boost

compensation

A6

SET

External Resistor Connection for Fast Charge Current Setting. Connect a resistor to this pin to set the

fast charge current. Other charge currents are set as a proportion of fast charge current based on I

2

C

register settings.

A7-A9

BAT

Battery Connection. Connect a 2s Li-ion+ battery from BAT to GND. Bypass to PGND with a parallel combination

of a 0.1 µF capacitor and an effective 10 µF - 30 µF capacitor. Keep the capacitors as close to BAT as possible and

keep the stray inductance and resistance of the trace from BAT to the battery terminal as low as possible.

B1

CC2

USB Type-C CC2. Connect to CC2 on USB Type-C connector.

B2

FSUS

Force Suspend Input. Logic-high on this pin causes the input limiter to open and input current from CHGIN is reduced

to zero. This pin is internally pulled to GND through a 470kΩ (typ) resistor and has no effect if FSUSMsk = 1.

B3

DGND

Digital Ground.

B4

V

TPU

External Voltage Input for TPU connection. Connect to external supply or V

CCINT

.

B5

BREG

Bypass for Internal Switching Converter Supply. Bypass with 1 µF capacitor to AGND.

B6-B9

SYS

System Load Connection. Connect SYS to the system load. Bypass to PGND with a parallel combination

of a 0.1 µF capacitor and an effective 22 µF capacitor. (Note: there is a diode between SYS and BAT)

C1

V

CONN

External V

CONN

Supply Input. Leave unconnected if not used.

C2

SCL

I

2

C Serial Clock Input. Connect an external pull-up resistor.

C3

V

CCINT

Bypass For Internal Analog Supply. Bypass with 1 µF capacitor to GND.

C4, D4,

D5

GND

Ground.

C5

BST

Charge Pump Connection. Connect a 0.1 µF capacitor between BST and LX.

C6, C7,

C8, C9

LX

Switching Node of Boost Converter. Connect a 1.5 µH or 2.2 µH inductor between LX and BYP. See

Applications Information section for more details.

D1

CC1

USB Type-C CC1. Connect to CC1 on USB Type-C connector.

D2

SDA

I

2

C Serial Data Input/Output. Connect an external pullup resistor.

D3

INT

Active-Low, Open-Drain Interrupt Output. Connect an external pullup resistor.

D6, D7,

D8, D9

PGND

Power Ground.

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

16

Bump Description

BUMP

NAME

FUNCTION

E1

CDN

USB Connector D-Input. Leave unconnected if not used.

E2

LED

LED Charging Status Indicator. Open-drain output indicating battery charging status. When LEDAuto = 1 and

a temperature fault is detected, the output is pulsed at 50% duty cycle for a period of 1.5s. When a charge

timer expires or SysFlt fault occurs, LED is pulsed at 50% for a period of 0.15s. When LEDAuto = 0, the open-

drain output is controlled by the LEDCtrl bit. Connect this pin to GND if unused.

E3

THM

Battery Temperature Thermistor Measurement Connection. This pin is used for NTC thermistor presence

detection and JEITA compliant temperature control.

E4

SFOUT

Output of overvoltage protected LDO powered from CHGIN. Bypass SFOUT with a 1 µF ceramic

capacitor to GND.

E5

CDIR

USB Cable Orientation Open-drain Output. When CC1 is active, this output is pulled low. Otherwise, this

output is high-impedance. Leave unconnected if not used.

E6-E9

BYP

Bypass Connection. Bypass to PGND with a parallel combination of a 0.1 µF capacitor and an effective

10 µF capacitor.

F1

CDP

USB Connector D+ Input. Leave unconnected if not used.

F2

TDP

USB Transceiver D+ Connection. Connect TDP to device microprocessor USB transceiver D+ line.

Leave unconnected if not used.

F3

TDN

USB Transceiver D- Connection. Connect TDN to device microprocessor USB transceiver D- line. Leave

unconnected if not used.

F4

BVCEN

External V

CONN

Supply Enable Output. Push-pull output between V

CCINT

and GND. Leave

unconnected if not used.

F5

NVP

Negative Voltage PFET Gate Control. Leave unconnected if not used.

F6-F9

CHGIN

USB Charger Input. Bypass this pin with a 1 µF capacitor to PGND.

Note: All capacitance values listed in this document refer to effective capacitance. Be sure to specify capacitors that will meet these

requirements under typical system operating conditions taking into consideration the effects of voltage and temperature.

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

17

Bump Description (continued)

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

18

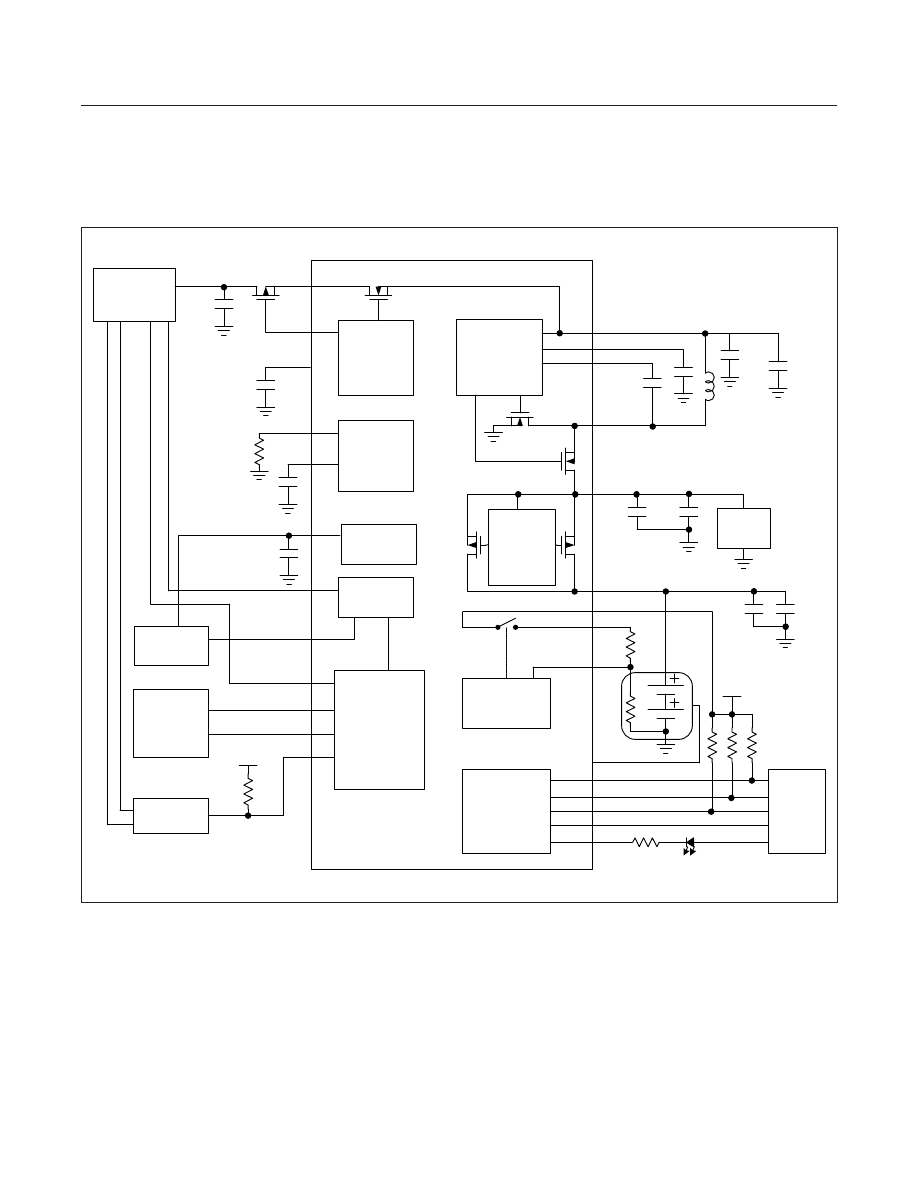

Block Diagram

Detailed Description

The MAX14748 is a battery charger with a Smart Power

Selector that safely charges two Li+ cell in accordance

with JEITA specifications*.

Input OVP

The MAX14748 CHGIN input is protected by an internal

N-channel FET. The device monitors the voltage at

CHGIN and, if CHGIN is greater than V

OVP

, switches

off the internal FET to prevent damage to the device.

If V

CHGIN

is above the overvoltage threshold or below

the USB valid voltage threshold, the MAX14748 enters

overvoltage lockout (OVLO). During OVLO, the internal

circuits remain powered, the SYSOK pin is high-impedance,

and an interrupt is asserted. During OVLO, the charger

turns off and the system load switch closes, allowing the

battery to power SYS.

Negative Voltage Protection (NVP)

The MAX14748 provides a gate protection circuit for an

external PFET that protects against negative voltages on

V

BUS

. NVP pin drives the gate of the external PFET. If a

negative voltage is present on V

BUS

, e.g., by a backwards

connector, the NVP turns off the external PFET, therefore

providing negative voltage protection.

Low Power Mode

The MAX14748 features a Low Power mode, which

reduces the battery current consumption from 25 µA to

140 µA. To enter Low Power mode, write 1 to LowPowEn

(Register 0x33[7]). To manually exit Low Power mode,

set LowPowAbort (Register 0x33[1]) to 1. If a DFP pullup

connect to CC1/CC2 is detected, the device automatically

exits Low Power mode and resumes normal operations.

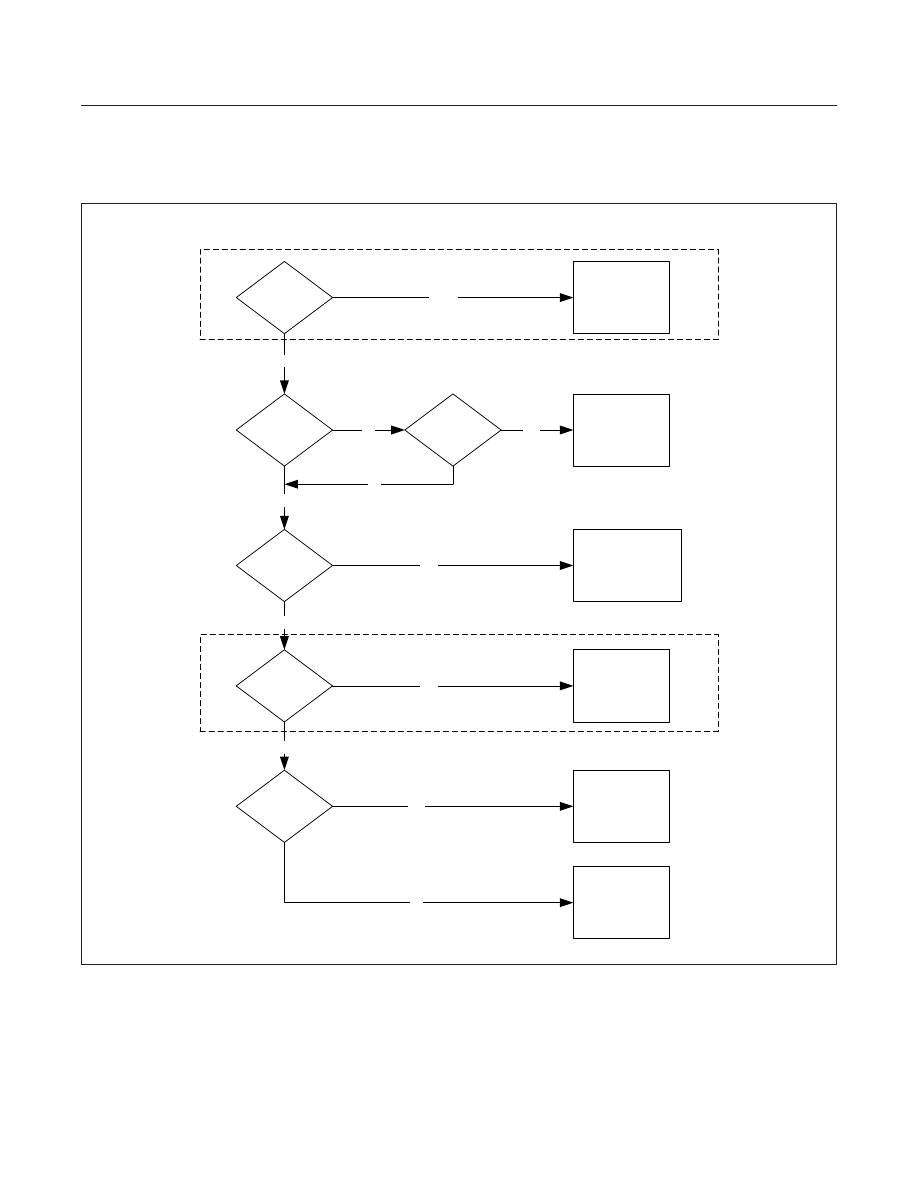

Input Current Limiter

The primary function of the input limiter is supplying

power from the external adapter at CHGIN to the system

load and battery charger. In addition, it performs several

other functions to optimize use of the available power

efficiently and safely, including:

1) CHGIN Input Current Limiting: The CHGIN input current is

limited to prevent input overload. The current limit can be

automatically selected through charger detection to match

the capabilities of the source. The result is indicated by

for more

details. It can also be manually set through CurLim1Frc

illustrates

how the current limit setting is selected.

2) Thermal Limiting: In case the die temperature

exceeds the normal limit (T

CHG_LIM

), the MAX14748

will attempt to limit temperature increase by reducing

the input current at CHGIN. In this condition, the

system load has priority over charger current, so the

input current is first reduced by lowering the charge

current. If the junction temperature continues to rise

and reaches the maximum operating limit (T

BUS_LIM

),

no input current is drawn from CHGIN and the battery

powers the entire system load.

3) Adaptive Battery Charging: While the system is

powered from CHGIN, the charger draws power from

SYS to charge the battery. If the total load exceeds

the input current limit, the battery supplies supplmental

current to the load.

4) Adaptive Input Current Limiting: If the MAX14748

input current limit is programmed in such a way that

the adapter voltage collapses due to resistive drop,

current limiting, or poor load transient response,

the AICL loop allows the MAX14748 to regulate the

input voltage above a value needed to ensure proper

operation.

the AICL block and associated parameters are found

in the registers 0x2C to 0x2E.

*JEITA (Japan Electronics and Information Technology Industries Association) Standard, A Guide to the Safe Use of Secondary

Lithium Ion Batteries on Notebook-Type Personal Computers, April 20, 2007.

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

19

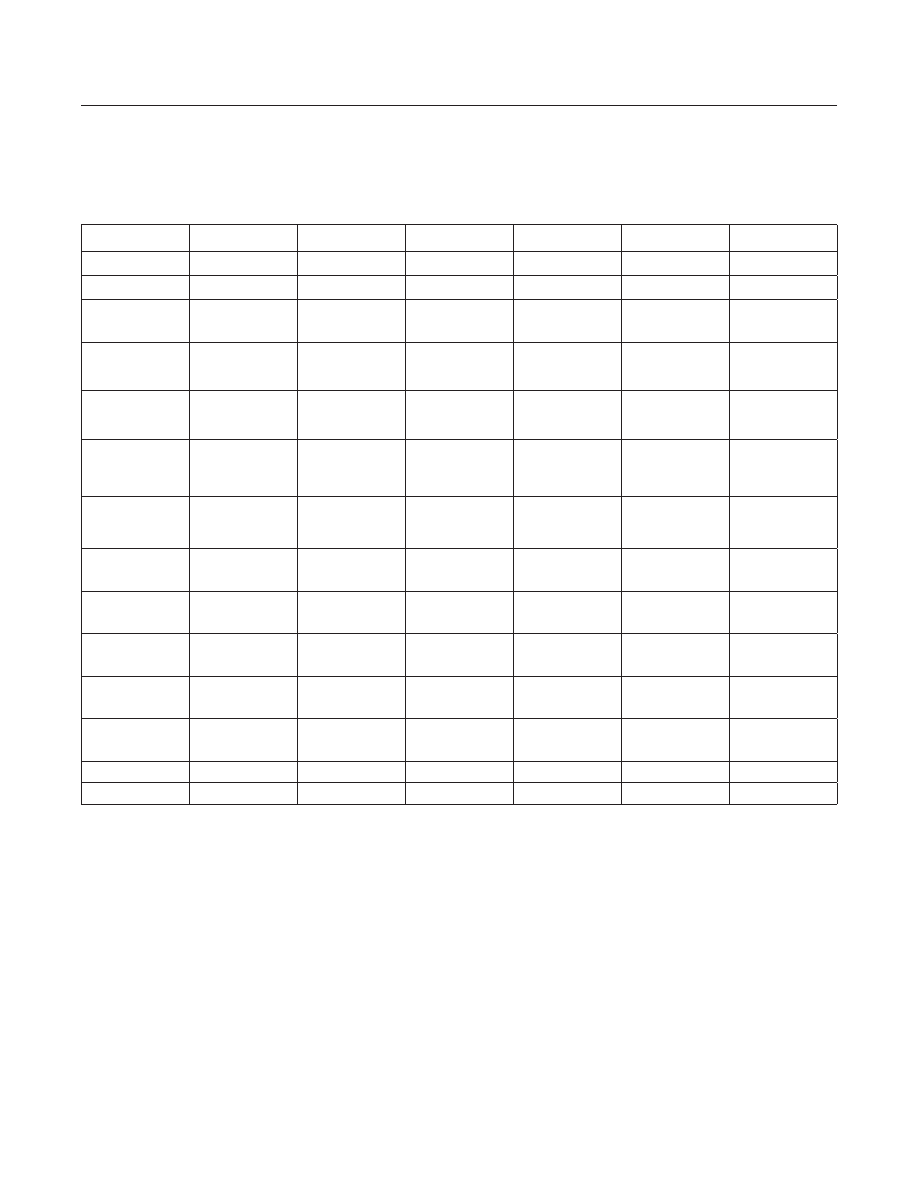

Table 1a. Automatic Input Current Limit Control

ChgTyp[1:0]

PrChgTyp[2:0]

CCIStat[1:0]

SDPMaxCur[1:0] CDPMaxCur[1:0]

I

LIM

SpvChgIlim[4:0]

xx

xxx

11 = 3A

00

0

3A

0x1D

11 = 1.5A

xxx

11 = 3A

xx

x

3A

0x1D

xx

110 = 3A

xx

xx

x

3A

0x1D

xx

101 = 2.4A

00 or

01 = 500mA or

10 = 1.5A

xx

x

2.4A

0x17

xx

100 = 2A or

001 = 2A

00 or

01 = 500mA or

10 = 1.5A

xx

x

2A

0x13

1x = 1.5A

000 or

010 = 500mA

00 or

01 = 500mA or

10 = 1.5A

xx

x

1.5A

0x0E

1x = 1.5A

000 or

010 = 500mA

or 011 = 1A

10 = 1.5A

xx

x

1.5A

0x0E

xx

011 = 1A

00 or

01 = 500mA

xx

x

1A

0x09

01 = 500mA

000 or 010 =

500mA

00 or

01 = 500mA

xx

x

0.5A

0x04

01 = 500mA

000

10 = 1.5A or

11 = 3A

01

x

0.5A

0x04

01 = 500mA

000

10 = 1.5A or

11 = 3A

10

X

1.0A

0x09

01 = 500mA

000

10 = 1.5A or

11 = 3A

11

x

1.5A

0x0E

10 = 1.5A

000

11 = 3A

xx

1

1.5A

0x0E

00

xxx

xx

xx

x

NA

NA

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

20

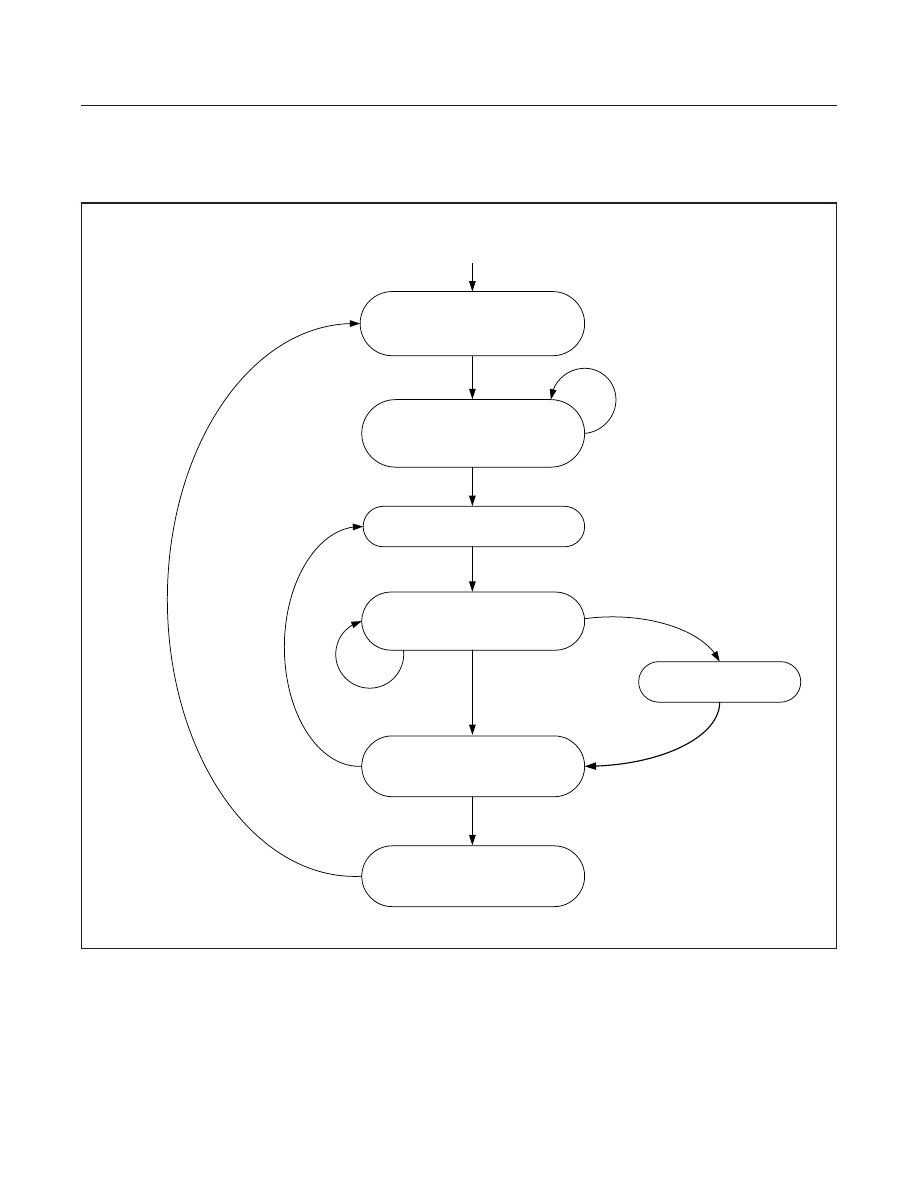

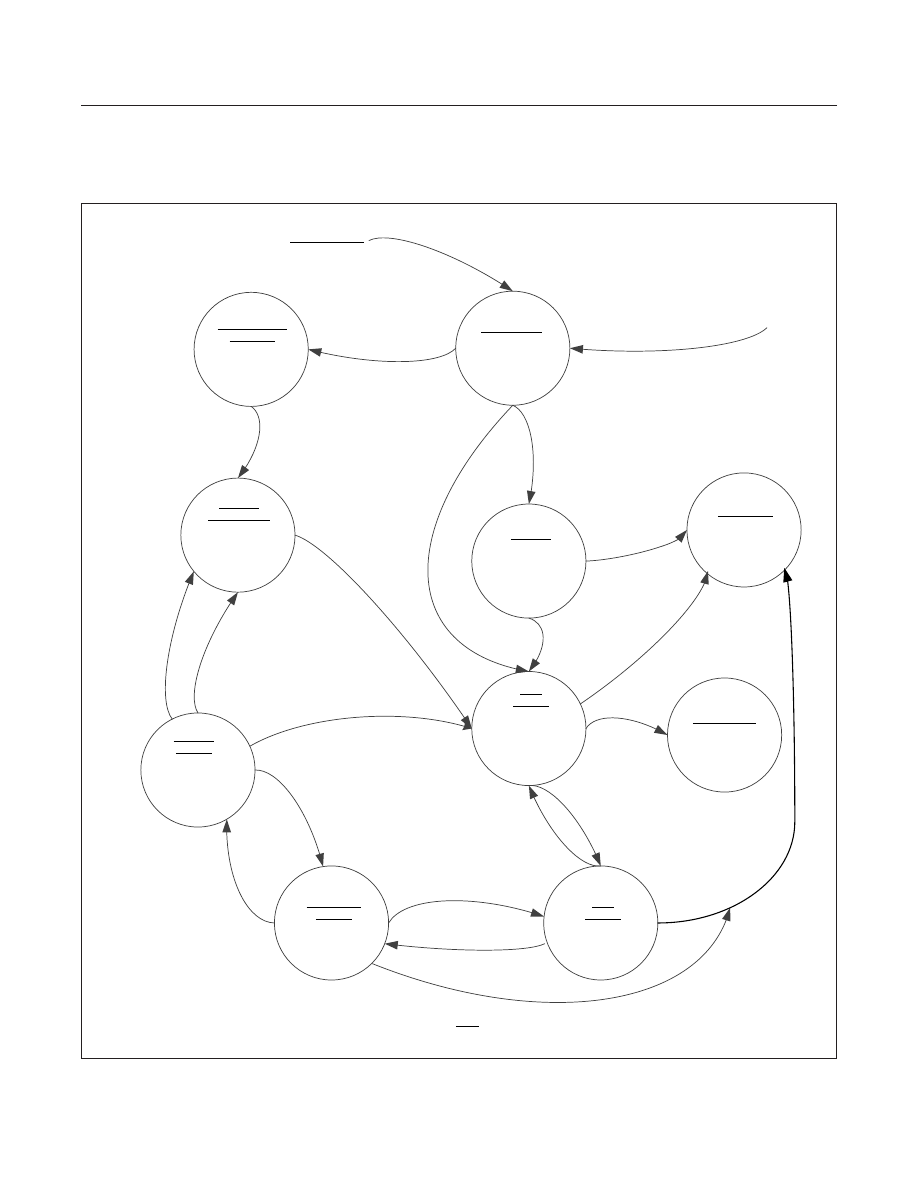

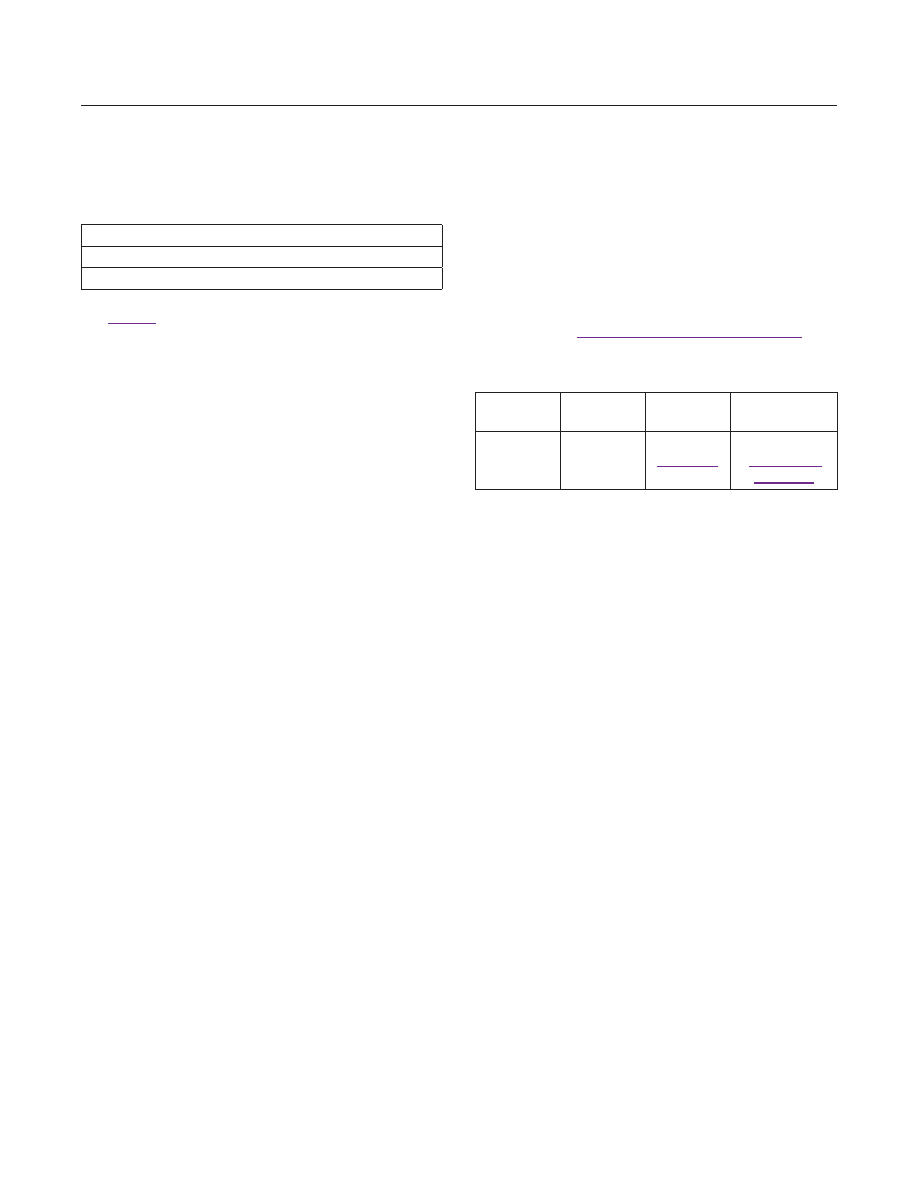

Figure 1. Input Current Limit Settings Flow Diagram

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

21

NO

NO

NO

YES

YES

T

DIE

> 150 °C

ILIM = 0

ILIM = 0

ILIM = WEAK BATTERY

CURRENT LIMIT

FSUS PIN =

HIGH

FSUSMsk = 1

WEAK

BATTERY

YES

YES

YES

NO

CurLim1Frc

ILIM = CurLim1Set[4:0]

value

AICLAbort = 0

AND AICLEn =1

ILIM SET BY AICL

ILIM = Auto

(USB-C/BC1.2)

NO

NO

FAULT CONDITION

MANUAL SETTING

YES

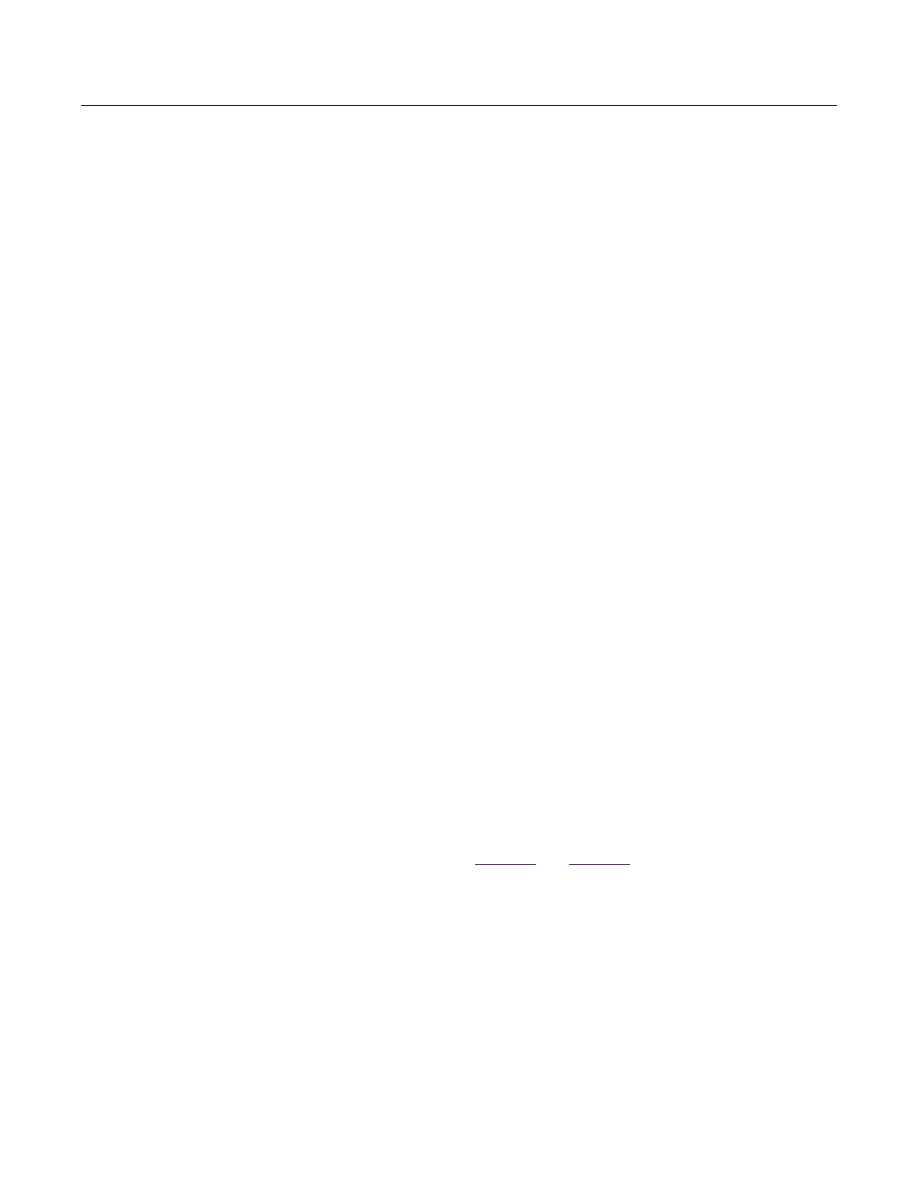

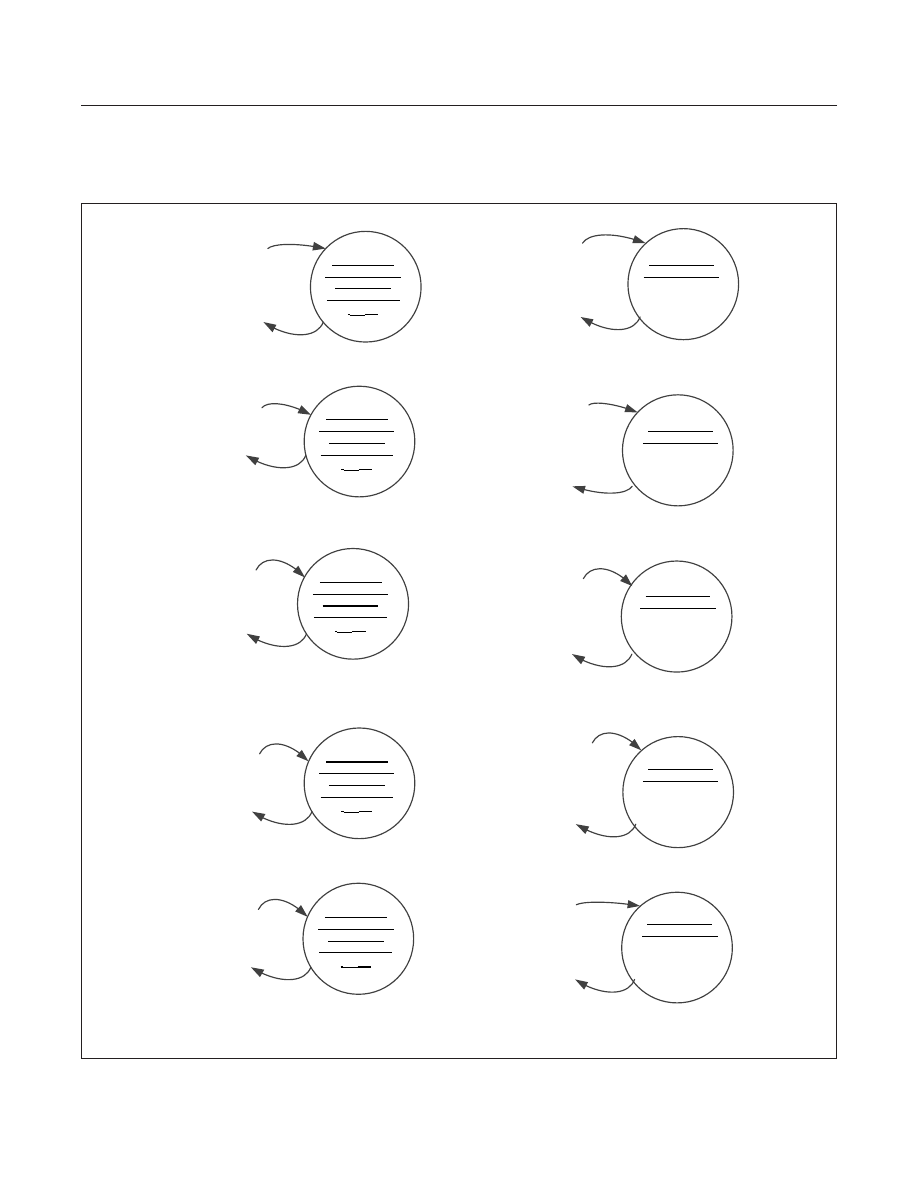

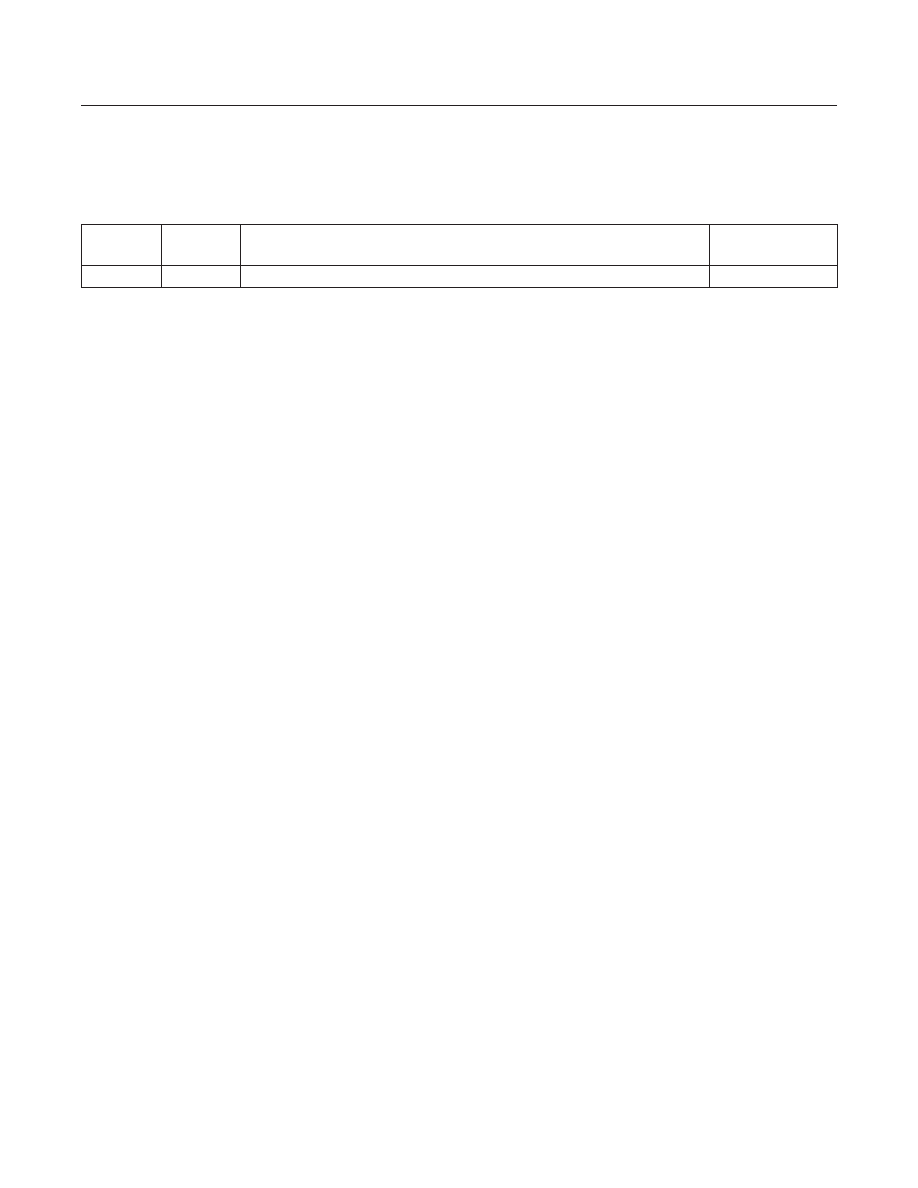

Figure 2. AICL Operation Flow Diagram

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

22

AICL INCREMENT

INPUT CURRENT = MIN

(STOP CURRENT, INPUT CURRENT + 100mA)

AICL PRECHECK

STOP CURRENT = AICLMaxI[4:0]

INPUT CURRENT = PREVIOUS SETTING

AICL IDLE

INPUT CURRENT = STOP CURRENT

AICL BLANK

INPUT CURRENT = 0,

STOP CURRENT = INPUT CURRENT - 100mA

VBDET MASKED AND OVP CLOSED

AICLAbort = 0 AND

AICLEn = 1

V

BYP

< V

BYPUVLO

AND TBLANK TIMEOUT

V

BYP

> V

BYPUVLO

AND

V

CHGIN

> V

BDET

V

BYP

< V

BYPUVLO

AICL OFF

STOP CURRENT = 500mA

MIN CURRENT = 100mA

INPUT CURRENT = PREVIOUS SETTING

AICL INIT

INPUT CURRENT = MIN CURRENT

V

BYP

> V

BYPUVLO

AND

INPUT CURRENT = STOP CURRENT

V

BYP

< V

BYPUVLO

TSTEP

TIMEOUT

AICLAbort = 1

AICLEn = 1

AICL NO CONNECTION

INPUT CURRENT = PREVIOUS SETTING

STOP CURRENT = 500mA

ChgStat[3:0] 0011

Boost Converter with Reverse Buck

Boost Mode

The MAX14748 boost converter operates as either a

current-limited voltage source, or current source, depending

on the charger operational state. When a valid USB voltage

is present at CHGIN, and the charger is disabled, V

SYS

is regulated to V

BAT

+ 400mV. If the charger is in

precharge mode, V

SYS

is regulated to V

PCHG

+ 400mV.

When the system is in fast-charge mode, the boost

converter operates as a current source, delivering

current into the SYS node that is shared by the battery

and system loads.

The boost converter current limit may be acted upon

by multiple system blocks, including the programmed

input current limit, thermal status, charging current, SYS

regulation voltage block, and battery termination voltage

block. The minimum requested current from these blocks

at any given time determines the active current limit in

the boost.

Reverse Buck Mode

The CHGIN-SYS switching converter may operate as a

buck converter when needed to supply a load attached to

CHGIN. The load may be a Type-C sink or some other

proprietary device.

If Type-C DRP operation is enabled, the buck converter

can be enabled by the Type-C state machine. The output

voltage of the buck can be programmed from 4V to 5.5V

in 0.1V steps by writing to BuckVSet[3:0], however, it is

not recommended to change the output voltage when the

buck is active.

The output of the buck converter turns off when a

fault occurs. The specific fault occurred is indicated by

DCDCILim, DCDCRunAway, DCDCPGood status bits

(register 0x04). See Register Descriptions for more

details. When the buck is disabled due to a fault, both

VBUSDet (register 0x07) and VSAFE0V (register 0x0A)

change to 0. After the fault condition is removed, the buck

converter can be restarted by writing 1 to CCSnkRst,

CCSrcRst, CCForceError, or USBCRset auto-reset bits.

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

23

Smart Power Selector

The Smart Power Selector seamlessly distributes power

between CHGIN, battery (BAT) and the system (SYS).

The basic modes of operation of the smart power selec-

tor are:

1. With a valid external power source:

a. The external power source at CHGIN is the

primary source of energy.

b. The battery is the secondary source of energy.

c. Energy delivery to SYS is the highest priority.

d. Any energy that is not required by SYS is available

to the battery.

2. With no power source available at CHGIN:

a. The battery is the primary source of energy.

b. Energy delivery to SYS has the highest priority.

3. With a Type-C Sink or other load present at CHGIN:

a. The battery is the primary source of energy.

b. Energy delivery to SYS is the highest priority.

c. Energy delivery to BYP is the second highest

priority.

4. SYS Regulation Voltage:

a. When the charger path is enabled and the

charger is disabled, V

SYS

is regulated to V

BAT

+

400mV and BAT switch is off.

b. When the charger is enabled but in a non-charging

state such as maitain charge done, thermistor

suspend, or timer fault, V

SYS

is regulated to

V

BAT

+ 400mV and BAT switch is off.

c. When the input charger path is enabled and the

battery is charging in prequalification, V

SYS

is

regulated to V

PCHG

+ 400mV. Charge current is

reduced when V

SYS

approaches V

PCHG

+ 200mV.

d. When the input charger path is enabled and the

battery is charging in fast-charge or maintain charge

done, the BAT switch is closed and V

SYS

= V

BAT

. In

maintain charge done state, the connection between

SYS and BAT acts as an ideal diode. Therefore,

when V

SYS

drops below V

BAT

, the BAT switch is

turned fully on and the battery supplements the SYS

load along with the current from CHGIN.

e. When the switching converter is enabled as a

reverse buck, the BAT switch is closed and

V

SYS

= V

BAT

.

Short-Circuit Protection

The MAX14748 provides short-circuit protection to the

power nodes. When SYS is shorted to ground, input

current from CHGIN is limited by boost converter current

limit. Note in this case, FET diode from BAT-SYS prevents

control of FET BAT-SYS current. Battery current is not

limited by the MAX14748 and a pack protector is needed

to limit the battery current.

When either BYP or CHGIN is shorted to ground, the current

from BAT is limited by the reverse buck converter.

USB Type-C 1.1

USB Type-C 1.1 UFP and DRP Support

The MAX14748 provides support for devices functioning as

a Upstream Facing Port (UFP) or Dual Role Port (DRP)

per the current USB Type-C 1.1 specification. When acting

as a power source in DRP mode, the MAX14748 can provide

a 5V V

BUS

on the CHGIN pin through operation of the

reverse buck converter. The USB Type-C V

CONN

supply

is provided externally via the V

CONN

pin, and switched

internally onto one of the CC pins. An open-drain output

pin, BVCEN, is provided to enable the external V

CONN

supply based on the Type-C state machine output.

BVCEN is a push-pull output between GND and V

CCINT

.

USB BC1.2 Compliant and Nonstandard Charger

Support

The BC1.2 charger detection and special charger detection

routine is embedded within the Type-C state machine.

The BC1.2 and Special Charger detection routine runs

always when the state machine enters the AttachWait.

SNK state of the USB Type-C 1.1 state-machine.

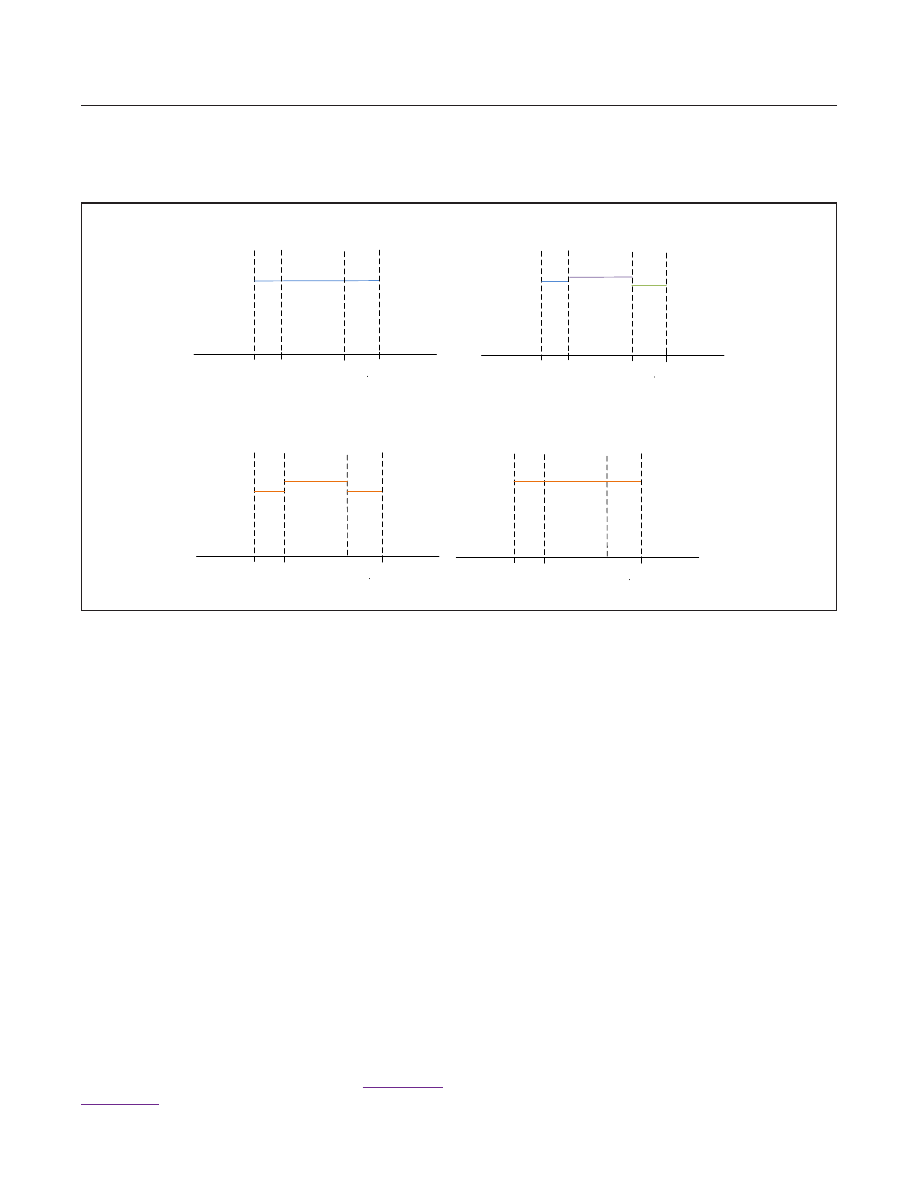

USB Type-C Adapter Insertion

and

depict the general timings when

a USB Type-C adapter is attached. For more information

on the behavior and timings of the USB Type-C 1.1 state-

machine, please refer to the USB Type-C specification.

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

24

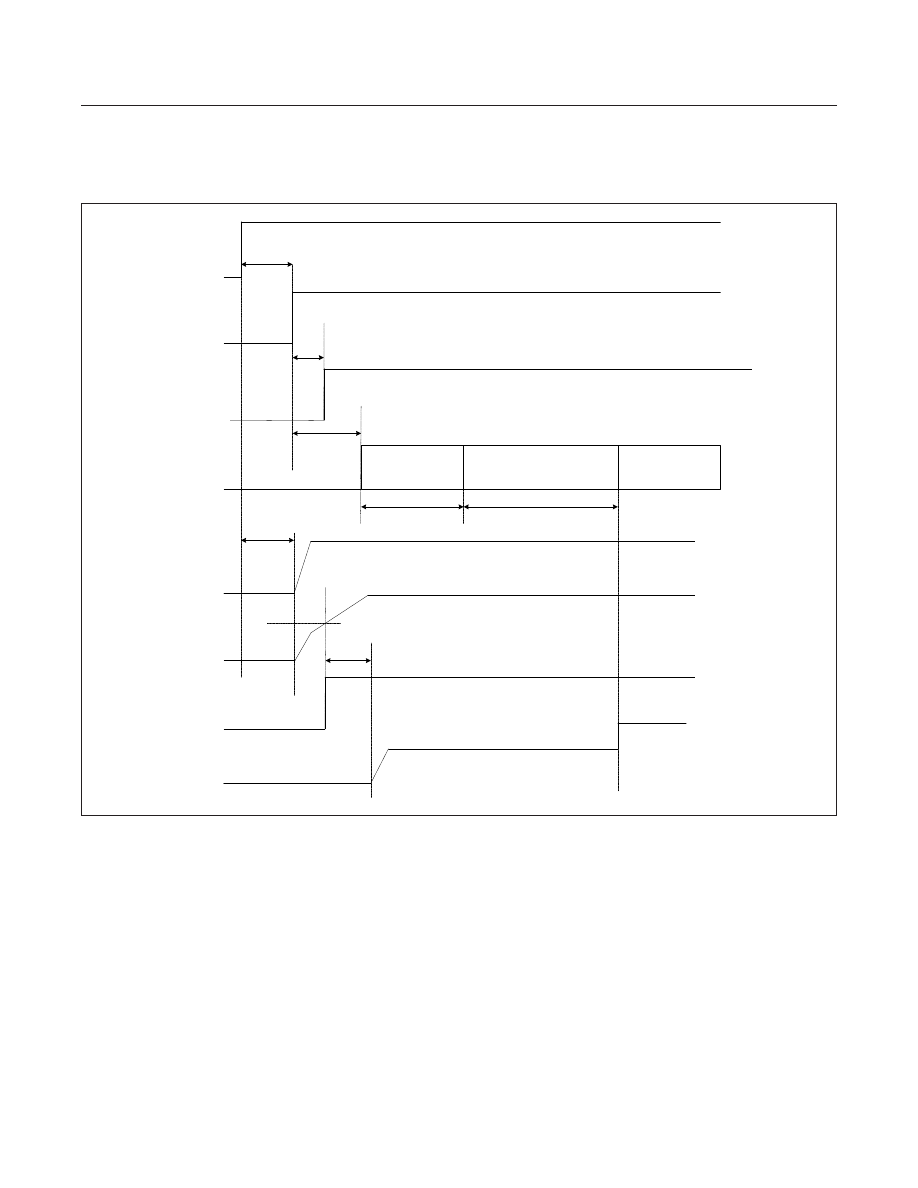

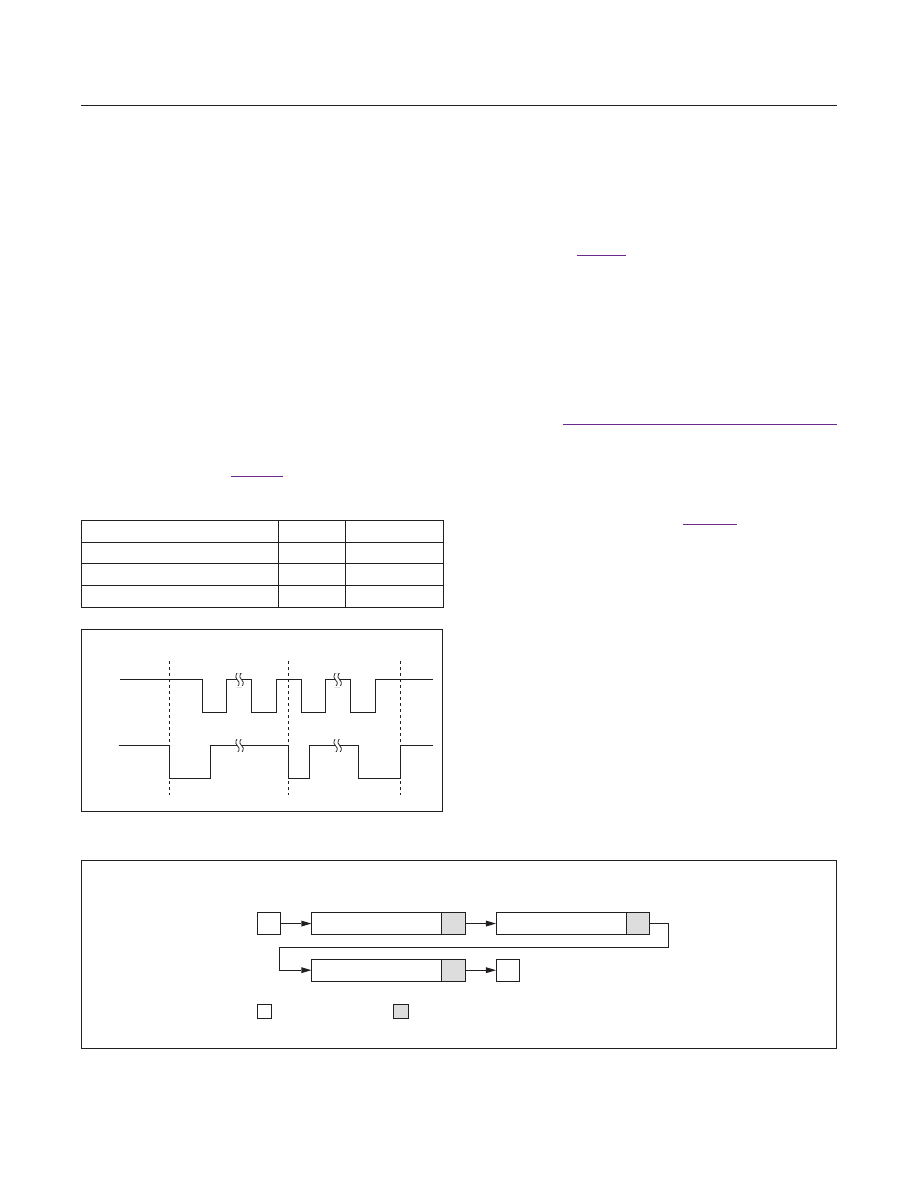

Figure 3a. Type-C Adapter Insertion (CHGINILimGate = 0)

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

25

BYP

V

SYS

SYSOK

I

BAT

35ms (TYP)

CHGIN

CC

0ms (MIN),

485ms (MAX)

DCD

CHARGER DETECTION

UPDATE CURRENT

CAPABILITY

10ms (TYP)

900ms(MAX)

250ms (MAX)

150ms (MIN),

485ms (MAX)

ChgDet

SFOUT

20ms (TYP)

V

SYSUVLO

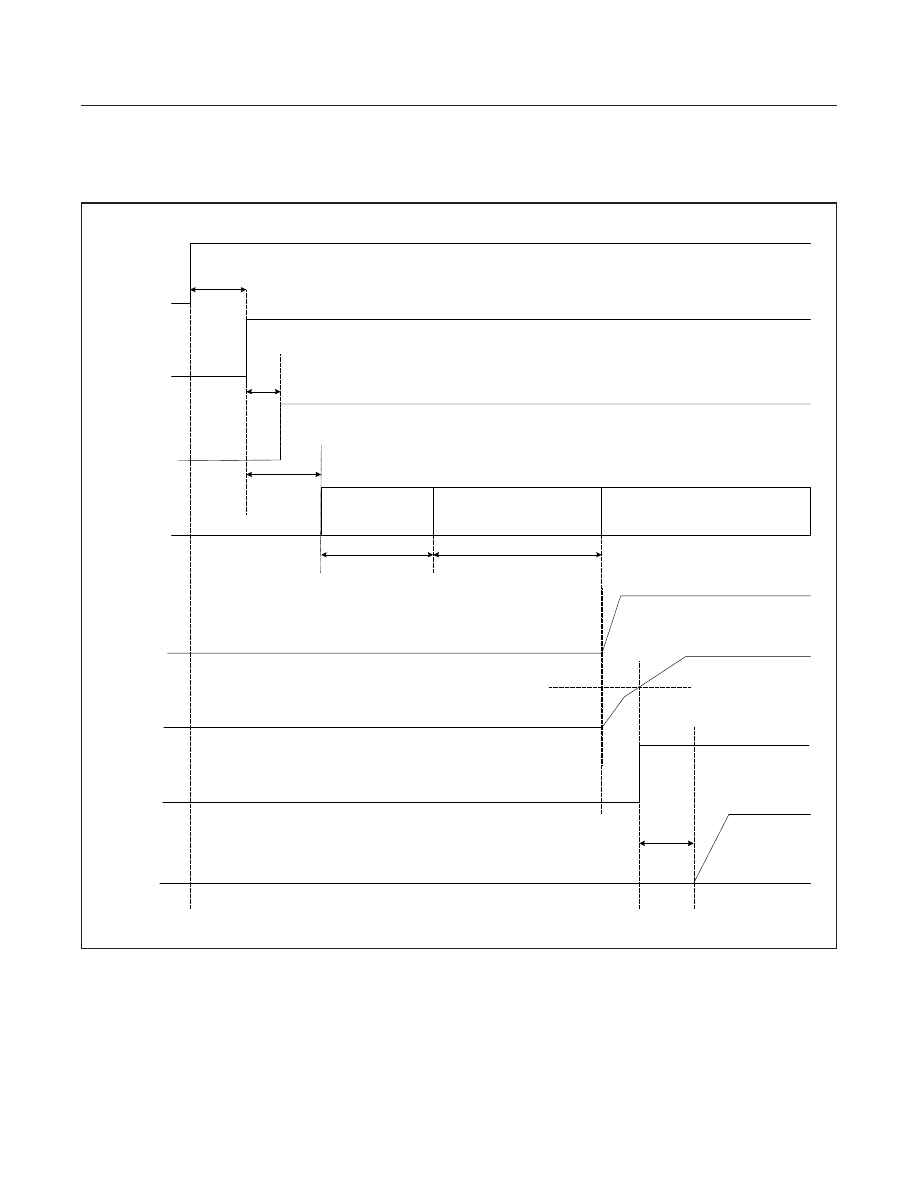

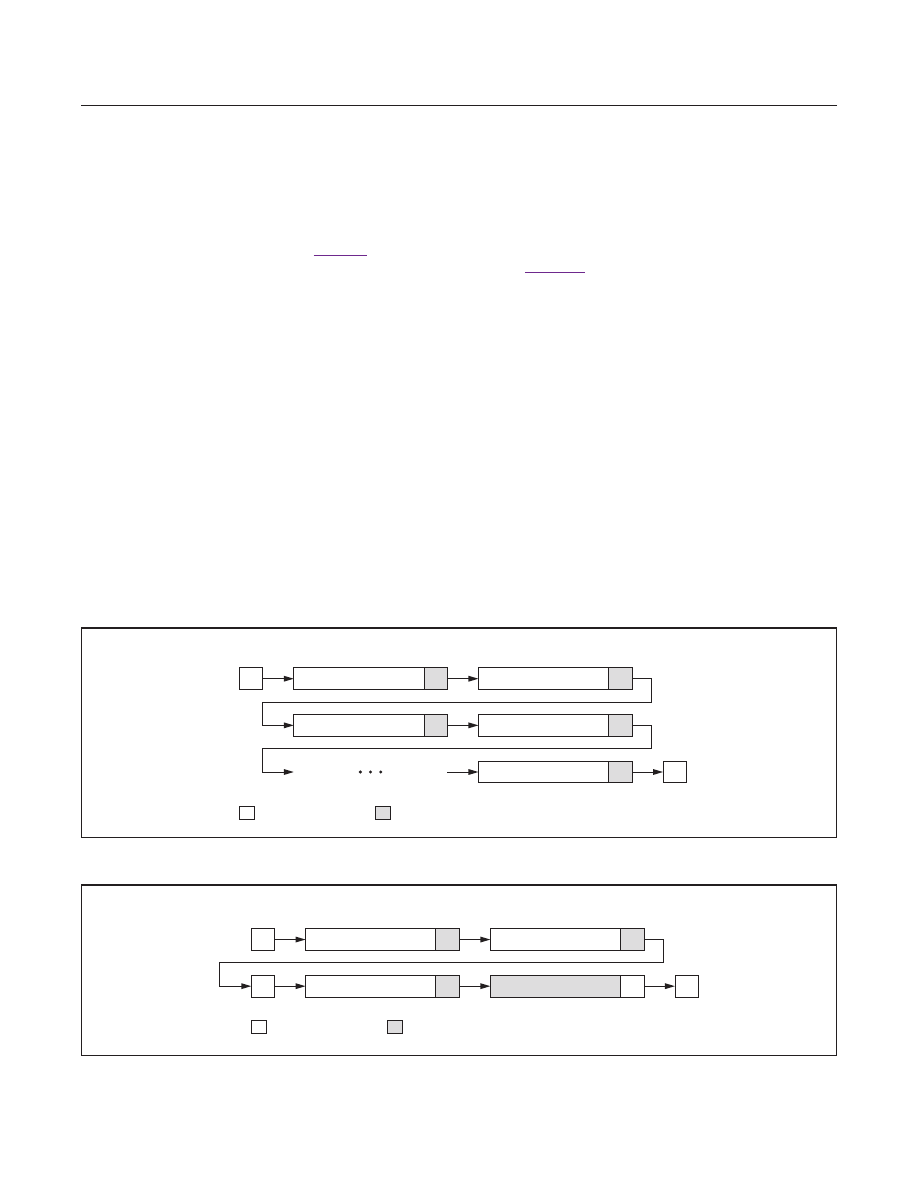

Figure 3b. Type-C Adapter Insertion (CHGINILimGate = 1)

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

26

BYP

V

SYS

SYSOK

I

BAT

CHGIN

CC

0ms (MIN),

475ms (MAX)

DCD

CHARGER DETECTION

UPDATE CURRENT CAPABILITY

10ms (TYP)

900ms(MAX)

250ms (MAX)

ChgDet

SFOUT

20ms (TYP)

V

SYSUVLO

35ms (TYP)

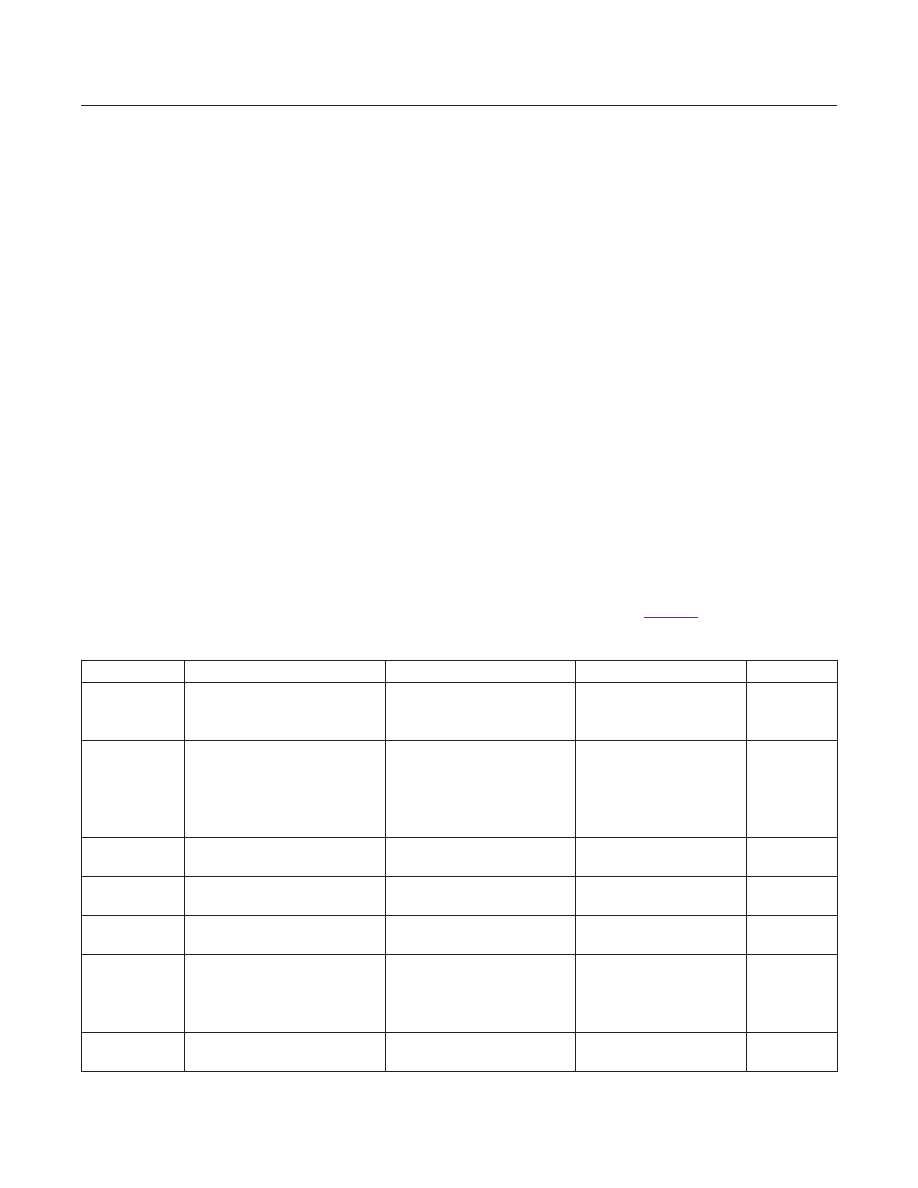

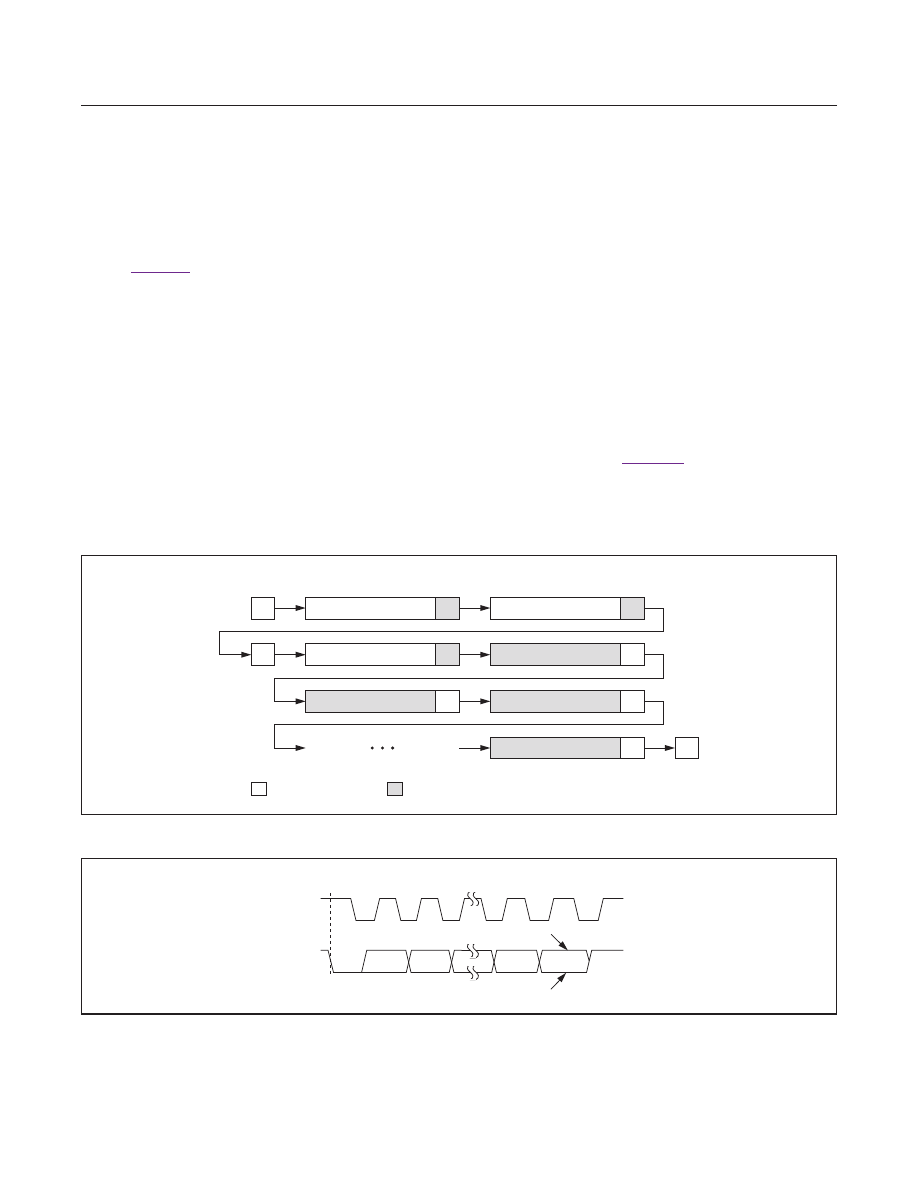

Figure 4. Battery Charger State Diagram

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

27

MAINTAIN

CHARGE DONE

ChgStat = 0110

LED = OFF

I

CHG

= 0

CHARGER OFF

ChgStat = 0000

LED = OFF

I

CHG

= 0

PREQUAL

ChgStat = 0010

LED = ON

I

CHG

= I

PCHG

FAST

CHARGE

(CONSTANT CURRENT)

ChgStat = 0011

LED = ON

I

CHG

= I

FCHG

**

FAST

CHARGE

(CONSTANT VOLTAGE)

ChgStat = 0100

LED = ON

MAINTAIN

CHARGE

ChgStat = 0101

LED = ON

I

CHG

< I

CHG_DONE

FRESH BATTERY

INSERTION

ChgStat = 0110

LED = 1s PULSE

I

CHG

= 0

TIMER FAULT

ChgStat = 0111

LED = 0.15s PERIOD

I

CHG

= 0

ChgEn = 1,

V

BAT

< V

BATREG

- V

BATRECHG

AND V

BAT

< V

PCHG_R

AND V

SYS

> V

BAT

+ TBDV

V

BAT

> V

PCHG_R

RESET CHARGE TIMER

V

BAT

< V

PCHG_R

VOLTAGE MODE

= 1*

VOLTAGE MODE

= 0*

RECOVER FROM FAULT RESET

CHARGE TIMER

ChgEn = 1,

V

BAT

>

V

BATREG

- V

BATRECHG

ChgEn = 1,

Fresh battery AND

V

BAT

>

V

BATREG

- V

BATRECHG

I

CHG

> I

CHG_DONE

and

VOLTAGE MODE = 1*

RESET CHARGE TIMER

I

CHG

< I

CHG_DONE

AND V

SYS

> V

SYS_LIM

AND T

DIE

< T

CHG_LIM

RESET CHARGE TIMER

I

CHG

> I

CHG_DONE

and

VOLTAGE MODE=0*

RESET CHARGE TIMER

t

CHG_TIMER

> t

MTCHG

AND

ChgAutoStp = 1

V

BAT

< V

BATREG

- V

BATRECHG

AND ChgAutoReSta = 1

AND V

SYS

> V

SYS_LIM

t

CHG_TIMER

> t

PCHG

t

CHG_TIMER

> t

FCHG

T

DIE

> T

BUS_LIM

OR V

BAT

> V

SYS

OR ChgEn=0

FROM ANY STATE

NOTES:

* VOLTAGE MODE IS AN INTERNAL SIGNAL

** CHARGE TIMER IS SLOWED BY 50% IF I

CHG

<I

FCHG

/2 AND PAUSED IF I

CHG

< I

FCHG

/5 ONLY IN FAST CHARGE CONSTANT CURRENT STATE

SYSTEM FAULT

ChgStat = 0111

LED = 0.15s PERIOD

I

CHG

= 0

JEITA VOLTAGE LIMITATION

AND ChgAutoStp = 1

V

BAT

< V

PCHG_R

ChgEn = 1,

V

BAT

< V

BATREG

- V

BATRECHG

AND V

BAT

> V

PCHG_R

AND V

SYS

> V

SYS_LIM

t

CHG_TIMER

> t

FCHG

LINEAR FAST

CHARGE

(CONSTANT VOLTAGE)

ChgStat = 0100

LED = ON

I

CHG

< 20% I

FCHG

V

BAT

< V

BATREG

- V

BATRECHG

Figure 5. Battery Charger State Diagram (continued)

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

28

PAUSE

CHARGE

TIMER

PAUSE

CHARGE

TIMER

PAUSE

CHARGE

TIMER

From PREQUAL

JEITA ERROR

To PREQUAL

NO JEITA ERROR

From FAST CHARGE CC

JEITA ERROR

From FAST CHARGE CV

JEITA ERROR

From FRESH BATTERY INSERTION ,

MAINTAIN CHARGE DONE ,

MAINTAIN CHARGE

JEITA ERROR

To CHARGER OFF

RESET CHARGE TIMER

NO JEITA ERROR

From PREQUAL

FLTIN = Low

To PREQUAL

FLTIN = High

From FAST CHARGE CC

FLTIN = Low

From FAST CHARGE CV

FLTIN = Low

To LINEAR FAST CHARGE

FLTIN = High

To CHARGER OFF

FLTIN = High

BATTERY FAULT

CHARGE SUSPEND

ChgStat = 1000

LED = 0.15s period

I

CHG

= 0

From FRESH BATTERY INSERTION ,

MAINTAIN CHARGE DONE ,

MAINTAIN CHARGE

FLTIN = Low

BATTERY TEMP

CHARGE SUSPEND

ChgStat = 0001

LED = 1.5s PERIOD

I

CHG

= 0

PAUSE

CHARGE

TIMER

PAUSE

CHARGE

TIMER

PAUSE

CHARGE

TIMER

BATTERY TEMP

CHARGE SUSPEND

ChgStat = 0001

LED = 1.5s PERIOD

I

CHG

= 0

BATTERY TEMP

CHARGE SUSPEND

ChgStat = 0001

LED = 1.5s PERIOD

I

CHG

= 0

BATTERY TEMP

CHARGE SUSPEND

ChgStat = 0001

LED = 1.5s PERIOD

I

CHG

= 0

BATTERY FAULT

CHARGE SUSPEND

ChgStat = 1000

LED = 0.15s period

I

CHG

= 0

BATTERY FAULT

CHARGE SUSPEND

ChgStat = 1000

LED = 0.15s period

I

CHG

= 0

BATTERY FAULT

CHARGE SUSPEND

ChgStat = 1000

LED = 0.15s period

I

CHG

= 0

To LINEAR FAST CHARGE

FLTIN = High

PAUSE

CHARGE

TIMER

From LINEAR FAST CHARGE

JEITA ERROR

To LINEAR FAST CHARGE

NO JEITA ERROR

From LINEAR FAST CHARGE

FLTIN = Low

To LINEAR FAST CHARGE

FLTIN = High

PAUSE

CHARGE

TIMER

BATTERY TEMP

CHARGE SUSPEND

ChgStat = 0001

LED = 1.5s PERIOD

I

CHG

= 0

BATTERY FAULT

CHARGE SUSPEND

ChgStat = 1000

LED = 0.15s period

I

CHG

= 0

To LINEAR FAST CHARGE

NO JEITA ERROR

To LINEAR FAST CHARGE

NO JEITA ERROR

Li-ion Battery Charger

Charger Overview

The MAX14748 utilizes a boost converter to generate

the necessary voltage to charge a 2s Li-ion battery from

a nominal 5V USB charger input. Depending on the

charging phase, the boost converter will operate as either

a current-limited voltage source or current source. The

charger is configured through a combination of external

components and I

2

C registers settings.

and

Battery Charger State Diagram.

Precharge

In precharge and charge termination phases, the boost

converter functions as a current-limited voltage source

and regulates V

SYS

to V

PCHG

+400mV. The battery is

charged through an internal linear charging path with a

maximum precharge current of 500mA (subject to thermal

limitations), programmable through I

2

C. The precharge/

fast-charge thresholds can be configured through register

0x1E and may not be less than the V

OVP

(max).

Fast Charge

In the fast-charge phase, the boost converter functions

as a current source delivering current into the SYS node.

The SYS and BAT nodes are shorted together through the

BAT-SYS FET, with a nominal resistance of 13mΩ (typ).

The fast-charge current is set by an external resistor, but

may be modified by the T_T_IFchg[2:0] bits in registers

0x1A and 0x1B. The fast-charge current resistor can be

calculated as R

SET

= K

SET

/I

FCHG

, where K

SET

has a

typical value of 10000A/A. The range of acceptable resis-

tors for R

SET

is 3.3kΩ to 100kΩ.

Charge Termination

During the charge termination phase, the battery current

is monitored across the BAT-SYS FET. To prevent a

false termination of charge, the charge done condition is

qualified by the state of the input current limit; if the input

current limit is currently active, the charge done condi-

tion is not triggered. The charge done condition is also

debounced for 140 µs in order to prevent transient system

currents from triggering an incorrect done condition.

Thermistor Monitoring

The MAX14748 provides highly programmable thermal/

JEITA charge management. All thermal/JEITA charge

configuration parameters are set via the ThermCfg reg-

isters 0x1A - 0x1C. The charger is managed by thermal

information only if JEITACtrSet = 1.

The battery pack temperature is measured from a divider

formed by a pull-up resistor, an optional parallel resistor,

and the battery pack thermistor. When required, the pullup

resistor is connected to an internal supply through the

TPU input, and the voltage on the THM pin is compared to

an internal threshold. The supply voltage for the divider

is applied to the V

TPU

pin and may be connected to an

external supply or to V

CCINT

. The pullup resistor may

be complemented with an additional parallel resistor to

allow matching to different thermistor nominal values

and charging cutoff temperatures, T1, T2, T3, and T4.

There are two sets of cutoff temperatures optimized for

a thermistor with Beta = 3380 (0 °C/10 °C/45 °C/60 °C or

0 °C/10 °C/25 °C/45 °C) which can be selected as factory

default options. These cutoff temperatures divide the

temperature range into three zones, T1_T2, T2_T3, and

T3_T4. The charger is always turned off at temperatures

outside these zones when any thermal monitoring mode

is enabled. If the system needs to measure the THM

temperature when not charging, the internal pullup switch

may be enabled via the JeitaCfgR[1:0] bits.

Charging may be optionally disabled in the T1_T2 and

T3_T4 zones through the T_T_EnSet bits. The charge

current in each zone may be modified through T_T_

IFchg[2:0]. Battery-voltage termination reduction may also

be selectively applied through the T_T_VFset bits. See

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

29

Weak Battery Operation

The MAX14748 supports the weak battery provision of

the USB 2.0 specification. If an SDP adapter is detected

and the battery voltage is less than the precharge threshold,

the input current limit is set to 500mA and a 2-minute

timer starts. After the 2-minute timer expires, the input

current limit is set to zero. Any time during the 2-minute

countdown, the system may turn off the weak battery

state machine and assert control of the input current limit

by setting WeakBatEn to 0.

Battery Detection

The MAX14748 offers battery detection by detecting the presence

of the battery thermistor. If the thermistor is not present, THM

is pulled high by the external pullup resistor, and BatDet is set

to 0 indicating that the battery is not connected.

Integrated USB 2.0 Analog Switch

A high-speed USB switch is integrated to provide the

host data access to the connected USB device when an

SDP or CDP port is detected. The analog switch may

be controlled manually or automatically by configuring

the AnSwCntl[1:0] bits in register 0x2F. When the ana-

log switch control is set to the auto control setting then

the CDN/CDP pins are connected to TDN/TDP only

when a SDP or CDP port is detected. (See

for further details.)

SFOUT LDO

The SFOUT LDO is powered directly from the CHGIN

input and may be used to power a USB transceiver, or

as an indicator signal that a SDP/CDP port is present.

The LDO will operate with CHGIN voltages greater than

V

BDET

. The output voltage of SFOUT is selectable as

either 5V or 3.3V through the SfOutLvl bit, depending on

the system preference. SFOUT may be programmed to

turn on automatically when an SDP or CDP is detected,

or placed in manual mode and turned on through an I

2

C

command. This supply is always available when CHGIN

is present.

Internal Supplies and Regulators

The MAX14748 has two internal power supplies: V

CCINT

and BREG. V

CCINT

and BREG are always present when

CHGIN or BAT is present. These supplies share a common

source, but bypassed separately. The V

CCINT

and BREG

supplies require external bypass capacitors and are

regulated to a nominal value of 4.3V (typ).

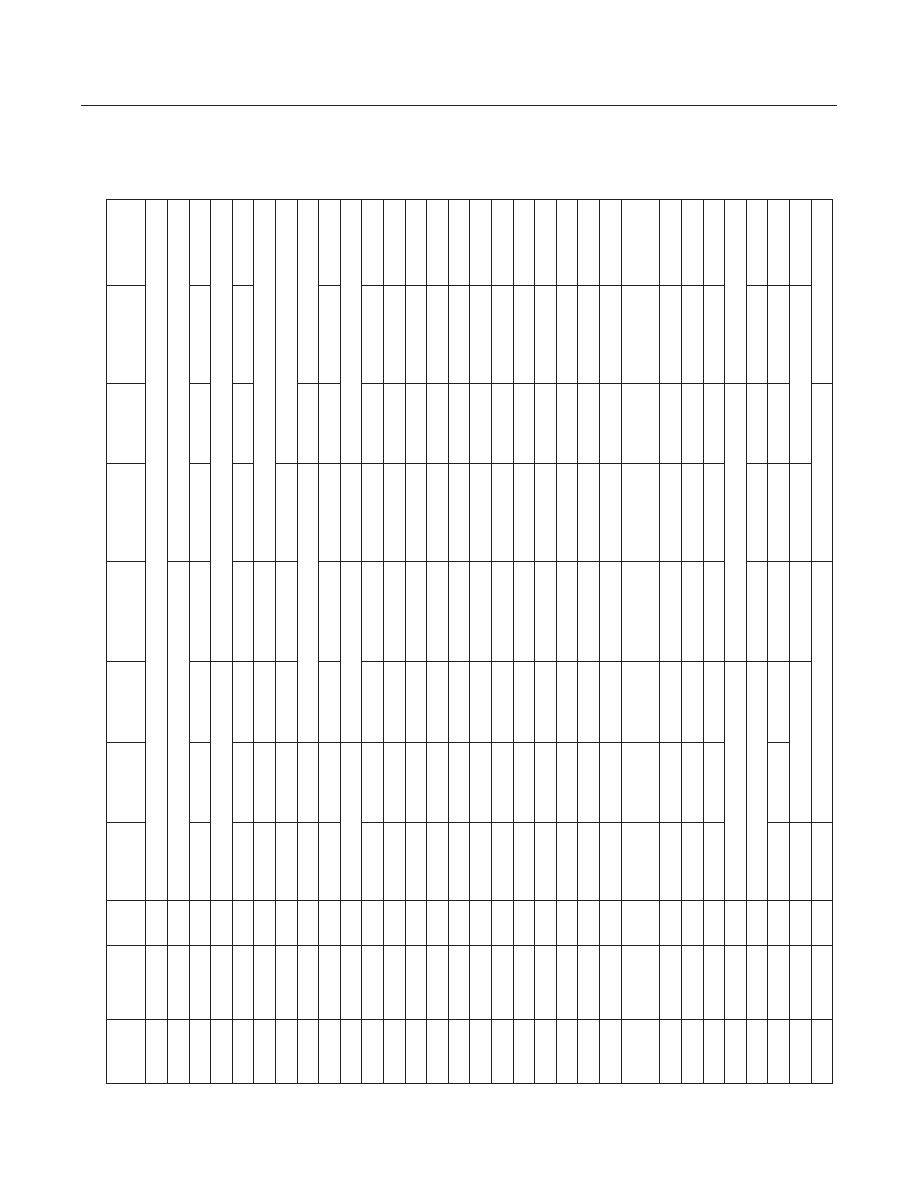

Figure 6. Thermistor Monitoring

MAX14748

USB Type-C Charger

www.maximintegrated.com

Maxim Integrated

30

T

1

T

4

TEMPERATURE ( ºC)

CHARGING

NO

CHARGING

NO

CHARGING

T

2

T

3

I

PCHG

PREQUAL:

V

BAT

<

V

PCHG

T

1

T

4

TEMPERATURE ( ºC)

CHARGING

NO

CHARGING

NO

CHARGING

T

2

T

3

T1T2IFchg[2:0]

FAST CHARGE CONSTANT CURRENT:

V

PCHG

< V

BAT

< V

BATREG

T2T3IFchg[2:0]

T

1

T

4

TEMPERATURE ( ºC)

CHARGING

NO

CHARGING

T

2

T

3

V

BATREG

REGULATED VOLTAGE

NO

CHARGING

T

1

T

4

TEMPERATURE ( ºC)

CHARGING

NO

CHARGING

T

2

T

3

V

BATREG

REGULATED VOLTAGE

NO

CHARGING

V

BATREG

- 300mV

T3T4IFchg[2:0]

T1T2ENset =1, T3T4ENset = 1

T1T2VFset = 1, T3T4VFset = 1

T1T2ENset =1, T3T4ENset = 1

T1T2VFset = 0, T3T4VFset = 0

V

BATREG

- 300mV

Device Control Interface

While the MAX14748 is primarily controlled by I

2

C, GPIO

control is also offered for specific functions. The following

GPIO control signals are provided (note that these signals

only apply when CHGIN is present):

1) FSUS (Input): Force Suspend. This pin enables the

host microcontroller to force the input current limit to

zero. When CHGIN is present, a logic-high on the pin

causes the input OVP FET at CHGIN to open and the

input current to MAX14748 is reduced to less than

2mA. This pin has no effect if FSUSMsk = 1.

2) FLTIN (Input): Battery Fault Input. This pin allows

the system or battery pack to place the charger into

a fault condition using a GPIO pin. See Register

0x35 description for more details.

3) CDIR (Open-Drain Output): USB Superspeed MUX

control. In USB Type-C plug configurations, it is

necessary to detect the orientation of the connector

and route the Superspeed lines accordingly. The pin

can be used to automatically configure a USB Super-

speed MUX according to the orientation information

contained in the integrated Type-C detection block.

(This information is also available through I

2

C) The

CDIR output is pulled to GND when the CC1 pin is

active on the Type-C connector, otherwise it is high-

impedance.

4) SYSOK (Open-Drain Output): With CHGIN present,

the SYSOK output is asserted if the boost regulator